### Synthesizing HW-SW Leakage Contracts for RISC-V Open-Source Processors

(to appear at DATE 2024)

Jan Reineke @

Joint work with

Gideon Mohr @ Universität des Saarlandes

Marco Guarnieri @ IMDEA Software

### The Need for New HW/SW Contracts

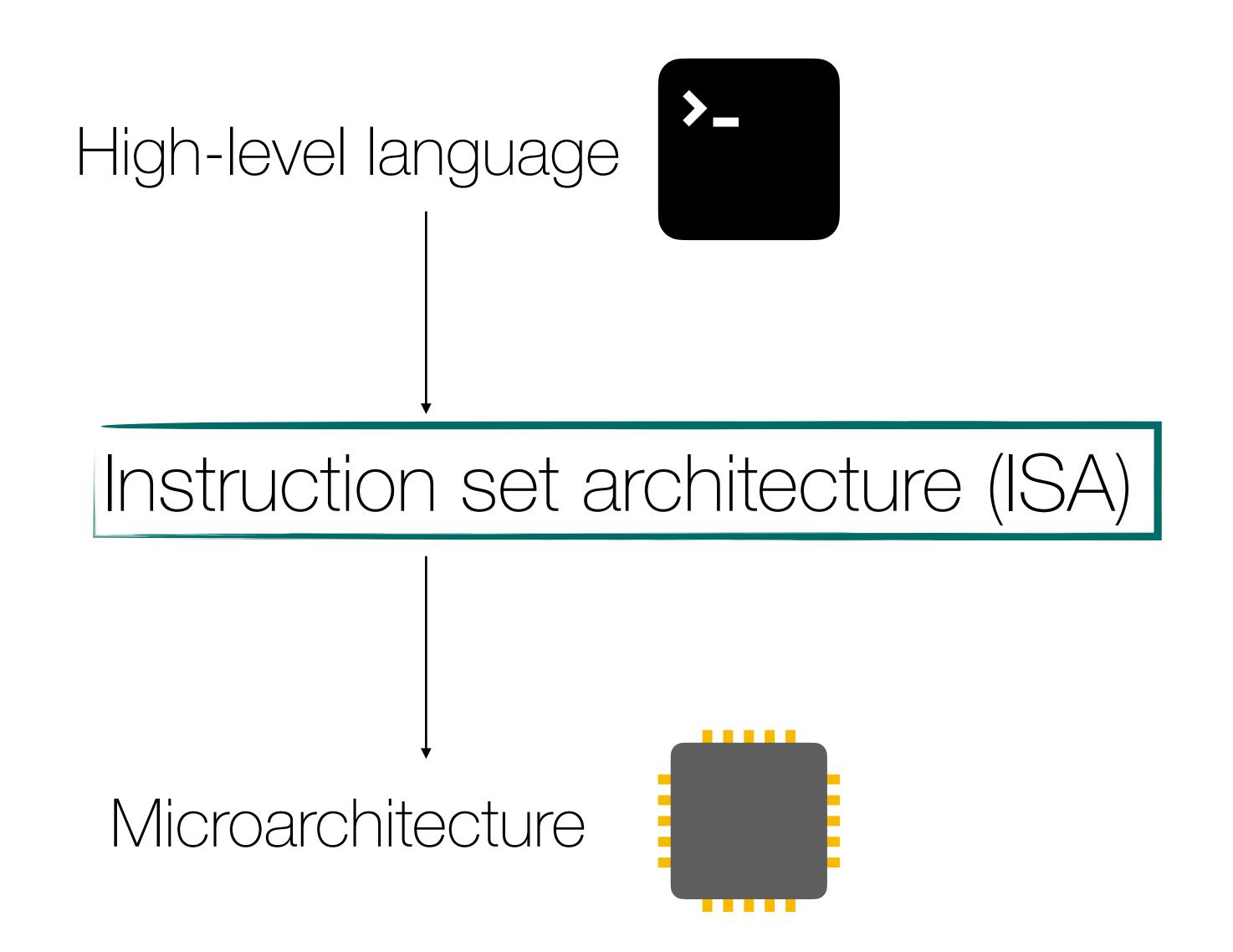

#### Instruction Set Architectures (ISAs): Benefits

#### Instruction Set Architectures (ISAs): Benefits

### Instruction Set Architectures (ISAs): Benefits

High-level language Instruction set architecture (ISA) Microarchitecture

High-level language No guarantees Instruction set architecture (ISA) about side channels Microarchitecture

High-level language No guarantees Instruction set architecture (ISA) about side channels Can implement arbitrary insecure optimizations as long as ISA is implemented correctly Microarchitecture

High-level language

Instruction set architecture (ISA)

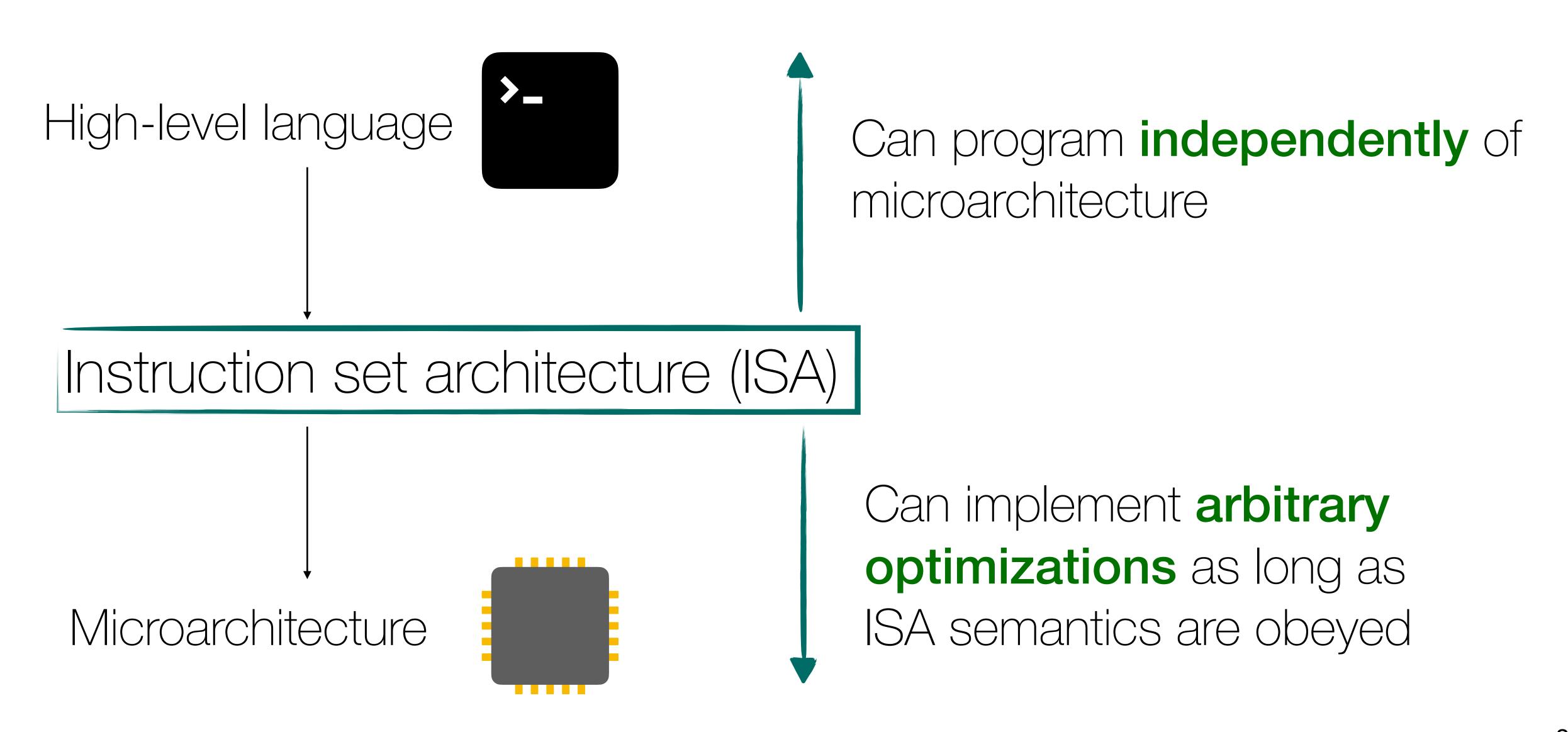

### No guarantees about side channels

Can implement arbitrary **insecure** optimizations as long as ISA is implemented correctly

High-level language

Impossible to program securely cryptographic algorithms? sandboxing untrusted code?

Instruction set architecture (ISA)

No guarantees about side channels

Can implement arbitrary **insecure** optimizations as long as ISA is implemented correctly

HW/SW Leakage contract = ISA + Leakage specification

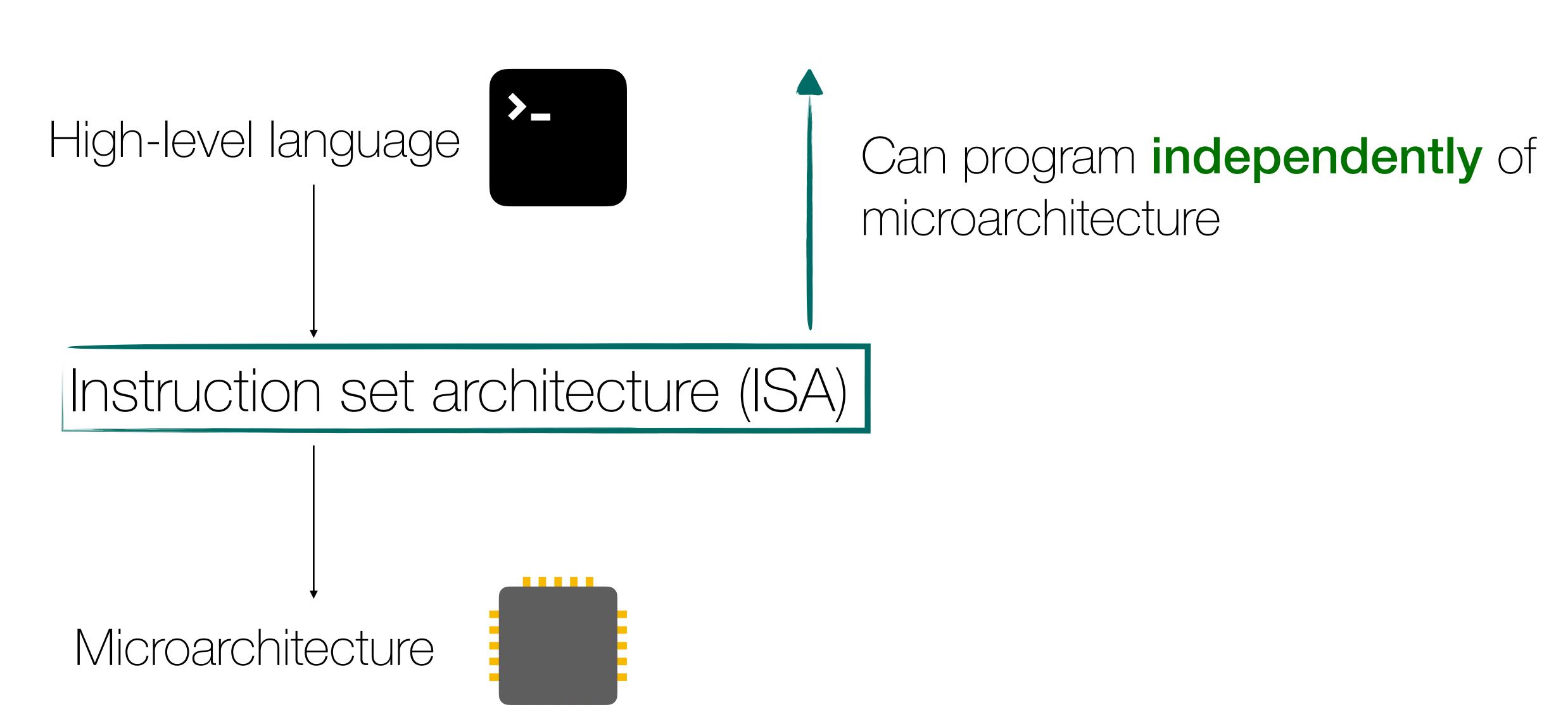

Can program securely on top of contract independently of microarchitecture

HW/SW Leakage contract = ISA + Leakage specification

HW/SW Leakage contract = ISA + Leakage specification

Can implement arbitrary insecure optimizations as long as contract is obeyed

Can program securely on top of contract independently of microarchitecture

HW/SW Leakage contract = ISA + Leakage specification

Captures possible leakage at ISA level

Can implement arbitrary insecure optimizations as long as contract is obeyed

#### Our prior work in this context

M. Guarnieri, B. Köpf, J. Reineke, and P. Vila Hardware-Software Contracts for Secure Speculation S&P (Oakland) 2021

Z. Wang, G. Mohr, K. v. Gleissenthall, J. Reineke, M. Guarnieri Specification and Verification of Side-channel Security for Open-source Processors via Leakage Contracts CCS (2023)

Can program **securely** on top of contract **independently** of microarchitecture

HW/SW leakage contract = ISA + Leakage specification

Captures possible leakage at ISA level

Can program securely on top of contract independently of microarchitecture

HW/SW leakage contract = ISA + Leakage specification

Captures possible leakage at ISA level

Can implement arbitrary insecure optimizations as long as contract is obeyed

Can program **securely** on top of contract independently of microarchitecture

HVV/SVV leakage contract = ISA + Leakage specification

Captures possible leakage at ISA level

Can implement arbitrary insecure optimizations as long as contract is obeyed

RISC-V Open-Source Cores

Can program **securely** on top of contract **independently** of microarchitecture

HW/SW leakage contract = ISA + Leakage specification

Captures possible leakage at ISA level

RISC-V Open-Source Cores

Can program **securely** on top of contract **independently** of microarchitecture

HW/SW leakage contract = ISA + Leakage specification

Captures possible leakage at ISA level

RISC-V Open-Source Cores

### Outline

- 1. Contracts and Contract Templates

- 2. Synthesis Goals and Methodology

- 3. Some Experimental Results

### Outline

- 1. Contracts and Contract Templates

- 2. Synthesis Goals and Methodology

- 3. Some Experimental Results

"For every multiplication the second operand leaks and for every memory access the memory address leaks."

Composition of Contract Atoms

"For every multiplication the second operand leaks and

for every memory access the memory address leaks."

Composition of Contract Atoms

"For every multiplication the second operand leaks and

for every memory access the memory address leaks."

Condition on ISA State

Composition of Contract Atoms

"For every multiplication the second operand leaks and

for every memory access the memory address leaks."

Condition on ISA State

Leakage of Part of ISA State

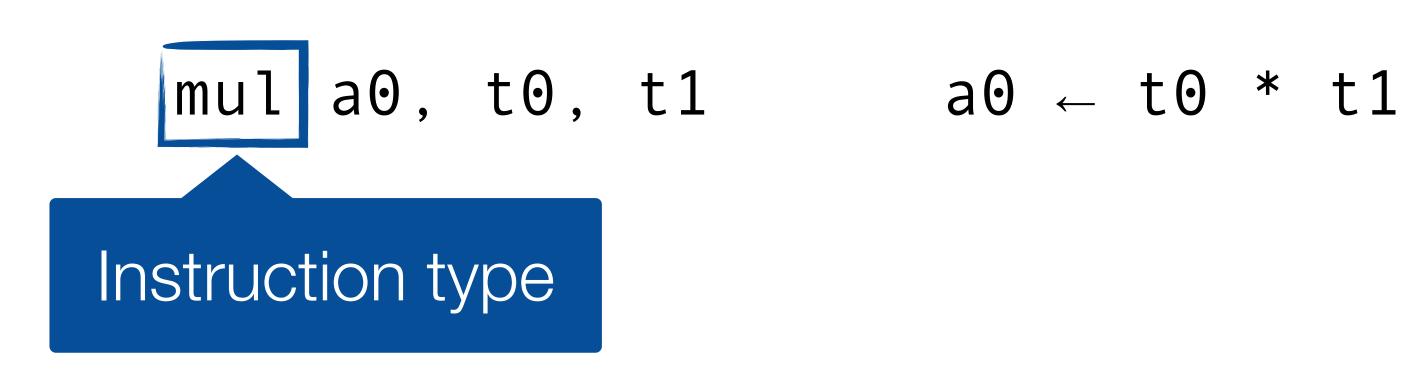

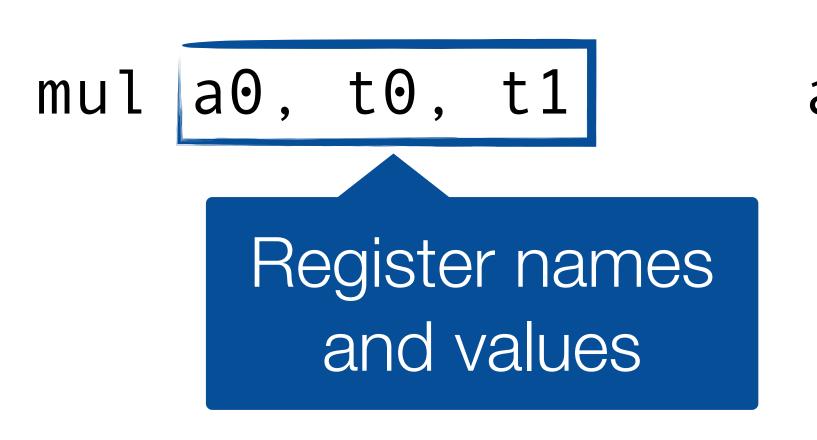

mul a0, t0, t1  $a0 \leftarrow t0 * t1$

Leakage sources:

Instruction type

$a0 \leftarrow t0 * t1$

- Instruction type

- Register names

- Register values

```

mul a0, t0, t1 a0 ← t0 * t1

```

- Instruction type

- Register names

- Register values

```

lw a1, -4(t2) a1 \leftarrow mem[t2 + (-4)]

```

```

lw a1, -4(t2)

Immediate values

```

mul a0, t0, t1

$a0 \leftarrow t0 * t1$

$a1 \leftarrow mem[t2 + (-4)]$

- Instruction type

- Register names

- Register values

- Immediate values

$a0 \leftarrow t0 * t1$

```

lw a1, -4(t2) a1 ← mem[t2 + (-4)]

Memory addresses

and values

```

mul a0, t0, t1

- Instruction type

- Register names

- Register values

- Immediate values

- Memory addresses

- Memory values

```

mul a0, t0, t1 a0 \leftarrow t0 * t1 lw a1, -4(t2) a1 \leftarrow mem[t2 + (-4)]

```

- Instruction type

- Register names

- Register values

- Immediate values

- Memory addresses

- Memory values

Contract Atom =

Contract Atom =

Condition based on Instruction Type

Contract Atom =

Condition based on Instruction Type

Applicable Leakage Sources

### Contract Atoms -What could possibly leak (non-speculatively)?

Contract Atom =

Condition based on Instruction Type

Applicable Leakage Sources

Several hundred contract atoms for RISC-VI+M

## Outline

- 1. Contracts and Contract Templates

- 2. Synthesis Goals and Methodology

- 3. Some Experimental Results

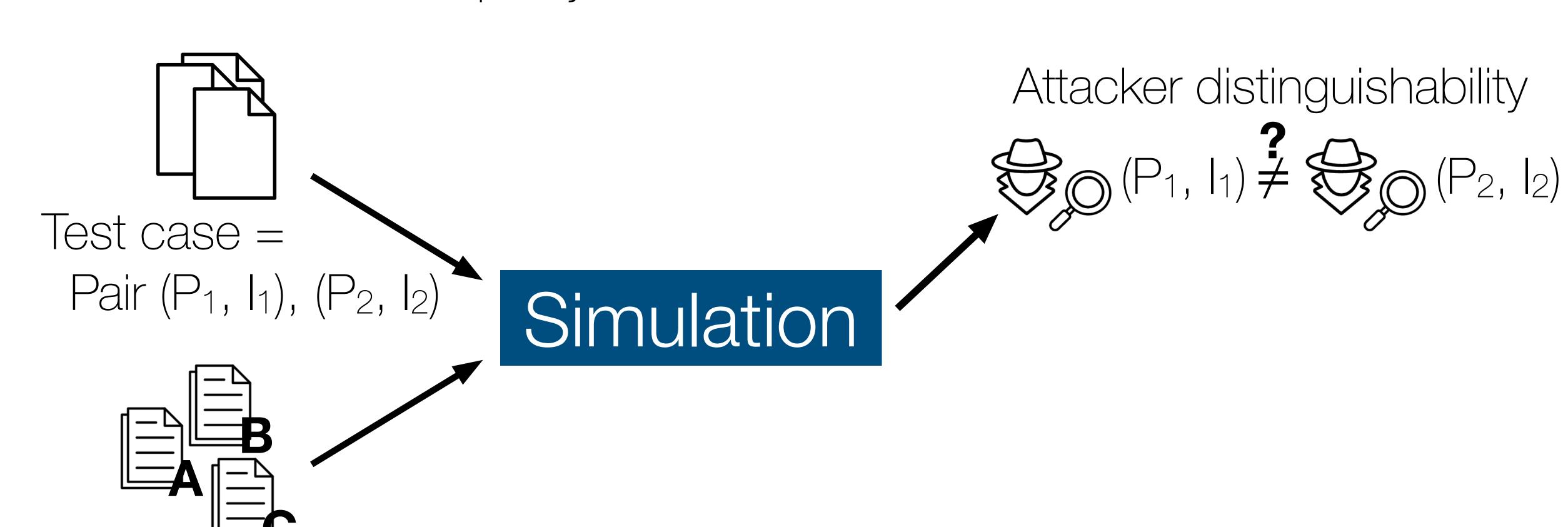

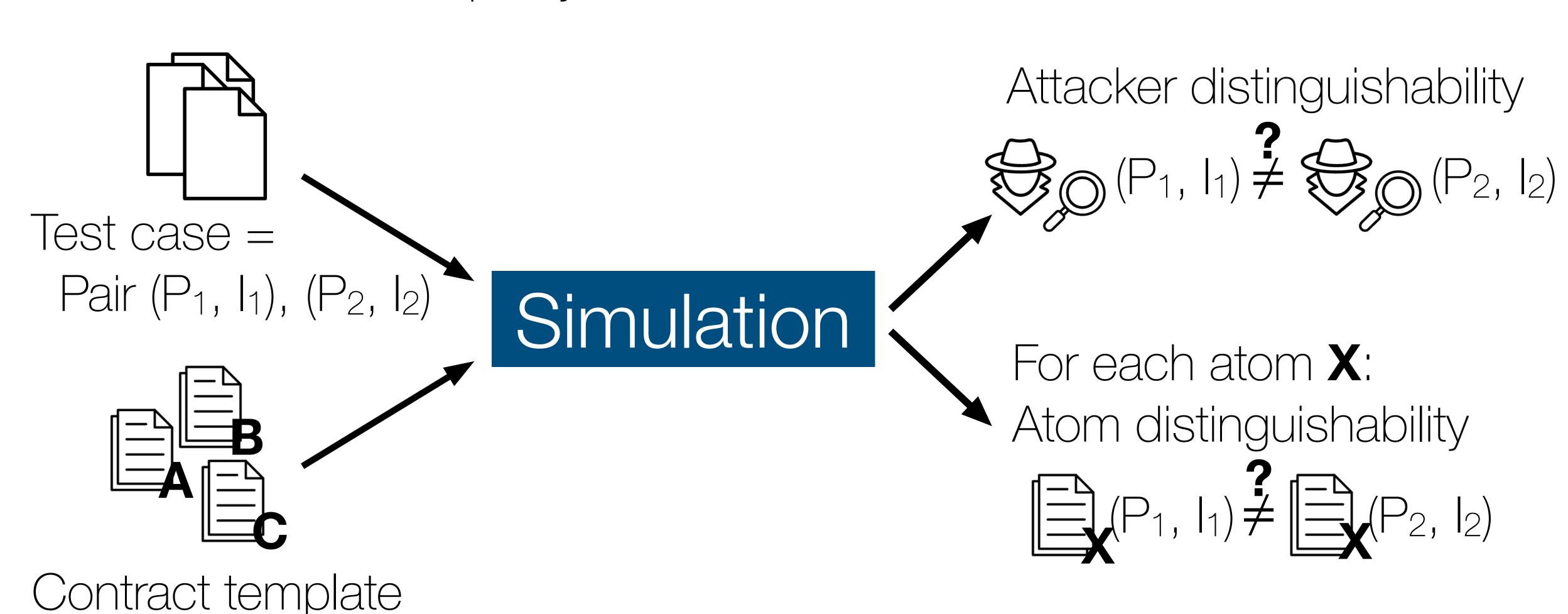

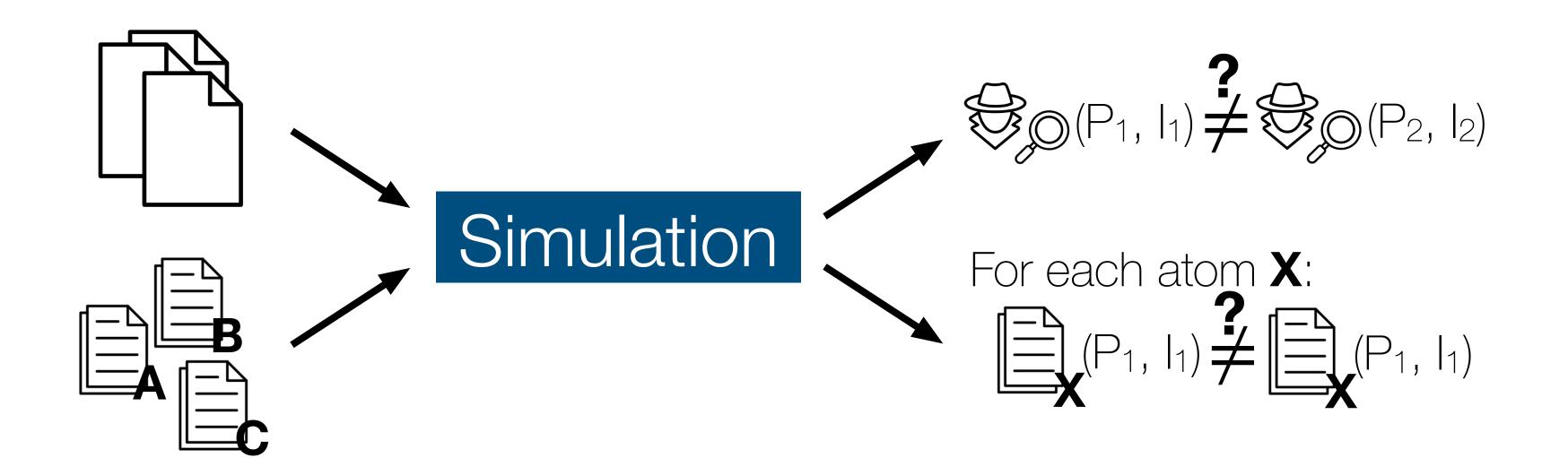

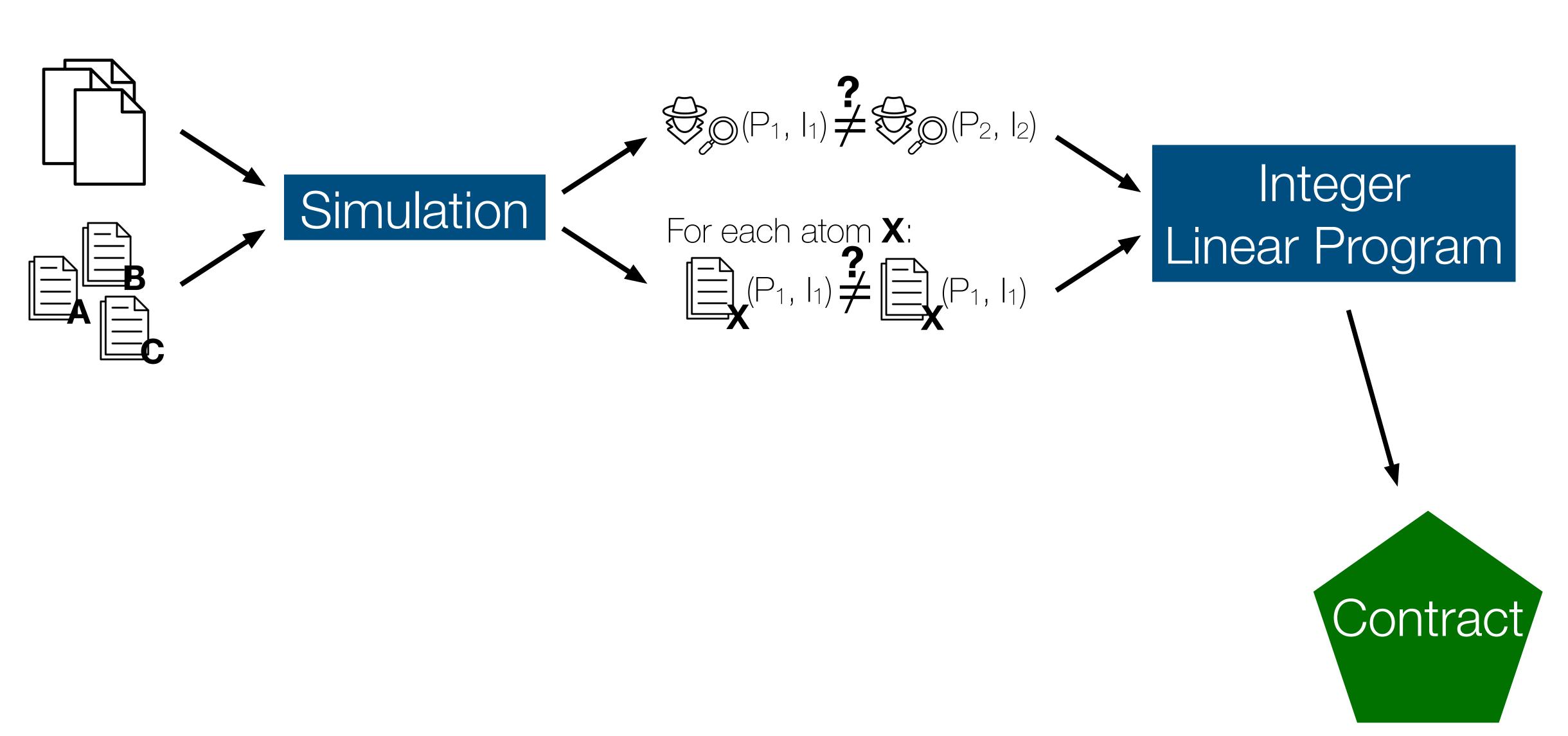

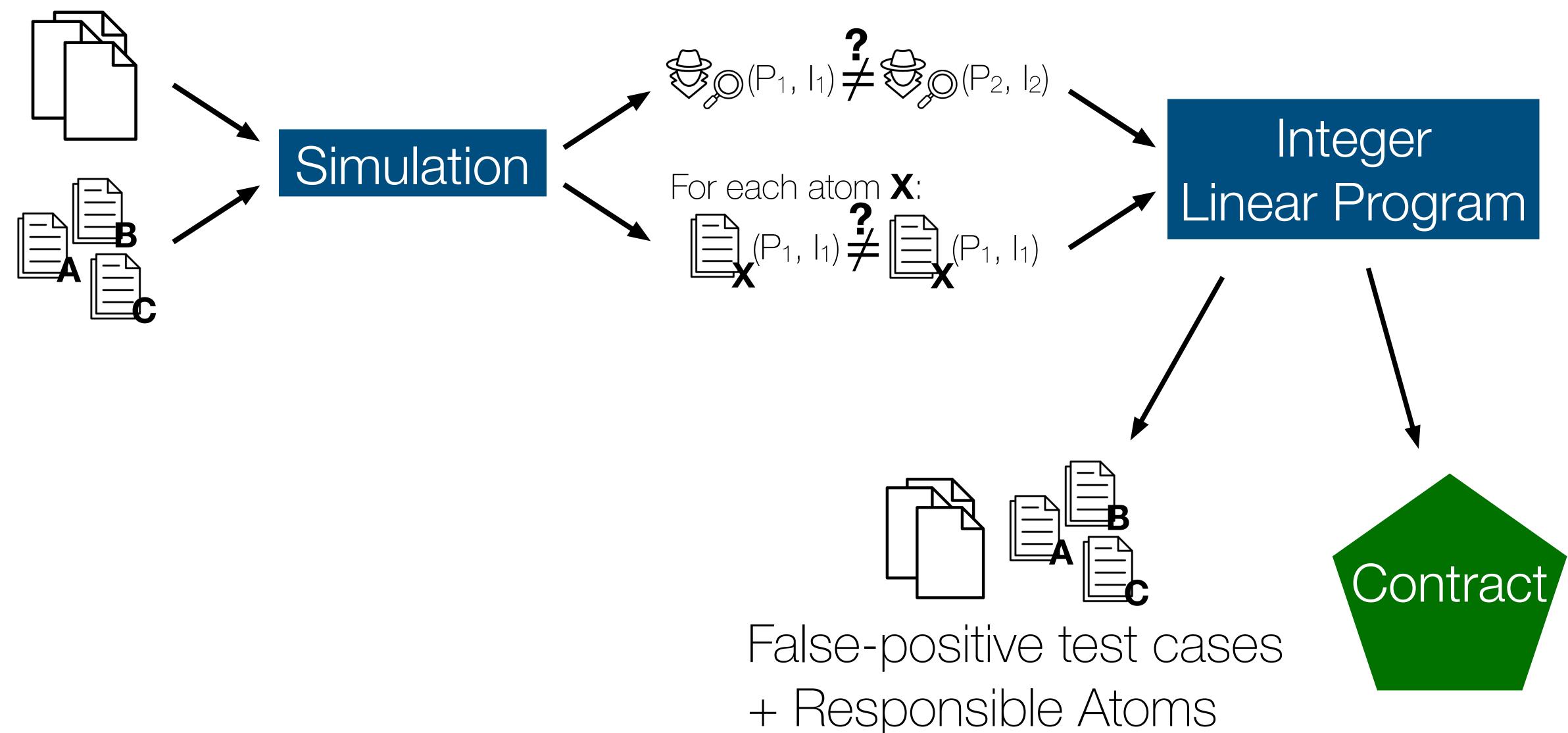

For a given processor, find contract from template s.t.:

For a given processor, find contract from template s.t.:

1. Processor satisfies contract

For a given processor, find contract from template s.t.:

1. Processor satisfies contract

For a given processor, find contract from template s.t.:

## 1. Processor satisfies contract

For any pair of programs and inputs  $(P_1, I_1)$  and  $(P_2, I_2)$ :

For a given processor, find contract from template s.t.:

## 1. Processor satisfies contract

For any pair of programs and inputs  $(P_1, I_1)$  and  $(P_2, I_2)$ :

$$P_1, I_1 \neq P_2 (P_2, I_2)$$

For a given processor, find contract from template s.t.:

## 1. Processor satisfies contract

For any pair of programs and inputs  $(P_1, I_1)$  and  $(P_2, I_2)$ :

For a given processor, find contract from template s.t.:

## 1. Processor satisfies contract

For any pair of programs and inputs  $(P_1, I_1)$  and  $(P_2, I_2)$ :

## 2. Contract is as precise as possible

As few programs and inputs (P, I) as possible s.t.:

For a given processor, find contract from template s.t.:

## 1. Processor satisfies contract

For any pair of programs and inputs  $(P_1, I_1)$  and  $(P_2, I_2)$ :

## 2. Contract is as precise as possible

As few programs and inputs (P, I) as possible s.t.:

$$P_1, I_1 \neq P_2, I_2$$

For a given processor, find contract from template s.t.:

## 1. Processor satisfies contract

For any pair of programs and inputs  $(P_1, I_1)$  and  $(P_2, I_2)$ :

## 2. Contract is as precise as possible

As few programs and inputs (P, I) as possible s.t.:

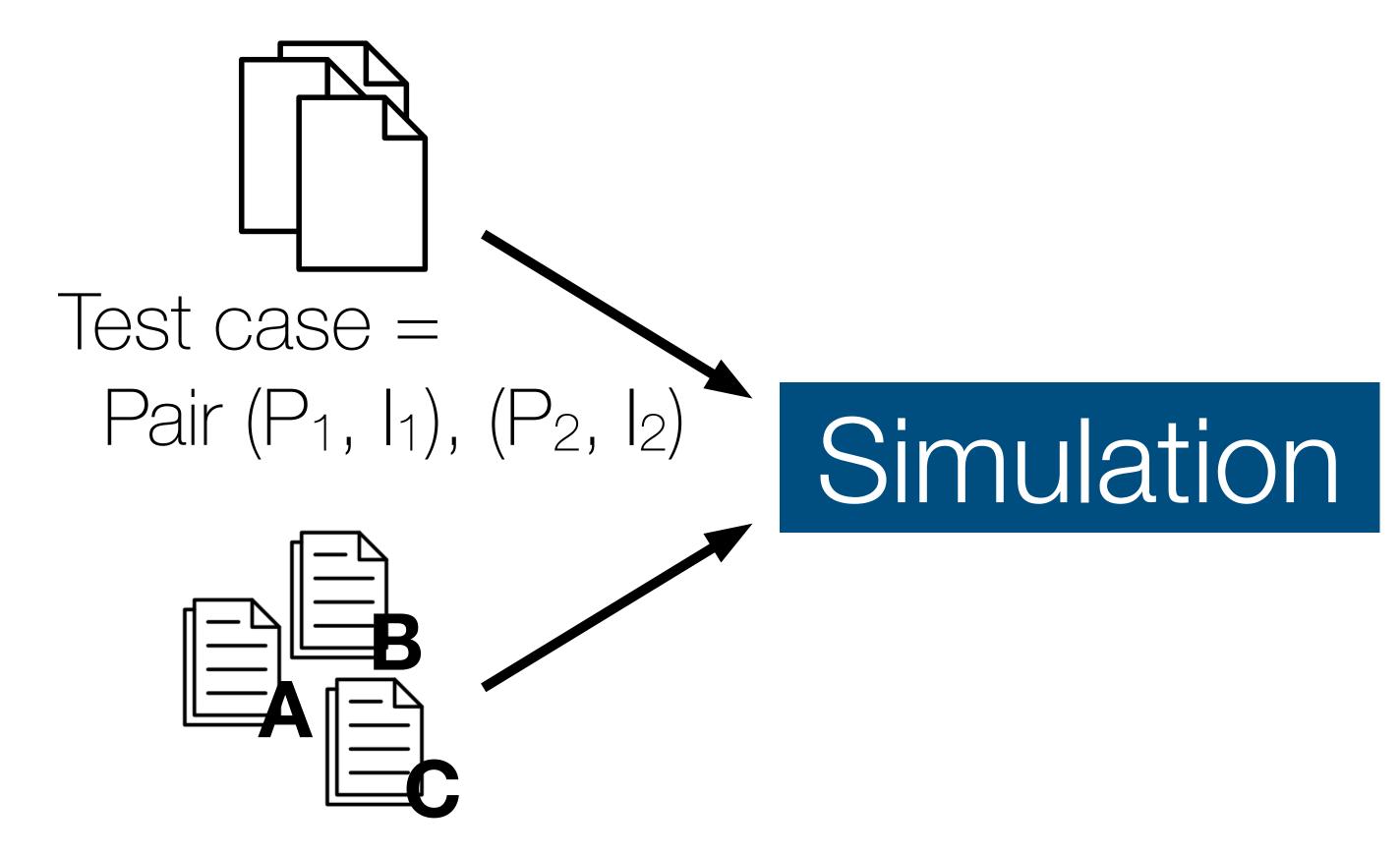

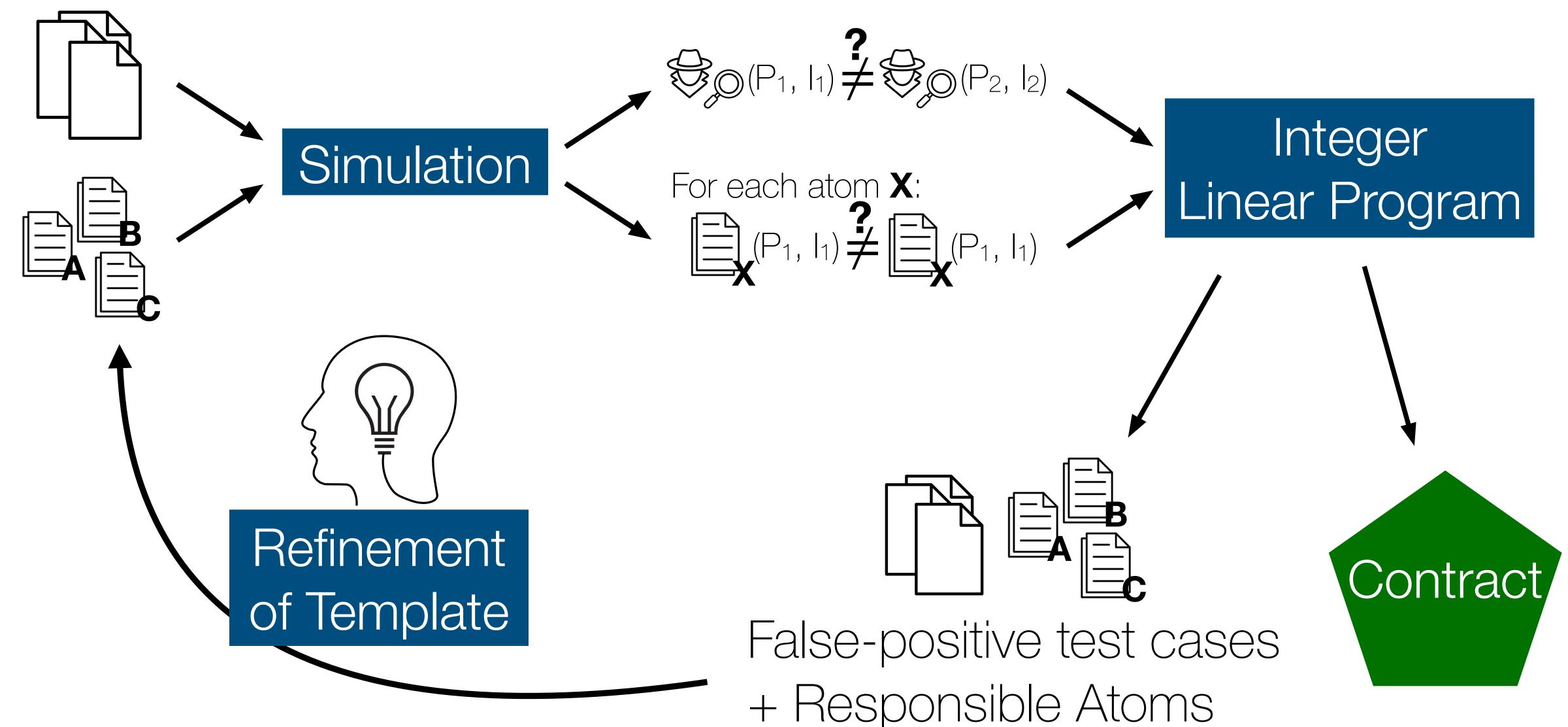

Use test cases as proxy for contract satisfaction

Use test cases as proxy for contract satisfaction

Contract template

Use test cases as proxy for contract satisfaction

Contract template

Use test cases as proxy for contract satisfaction

## Outline

- 1. Contracts and Contract Templates

- 2. Synthesis Goals and Methodology

- 3. Some Experimental Results

### **Experimental Evaluation**

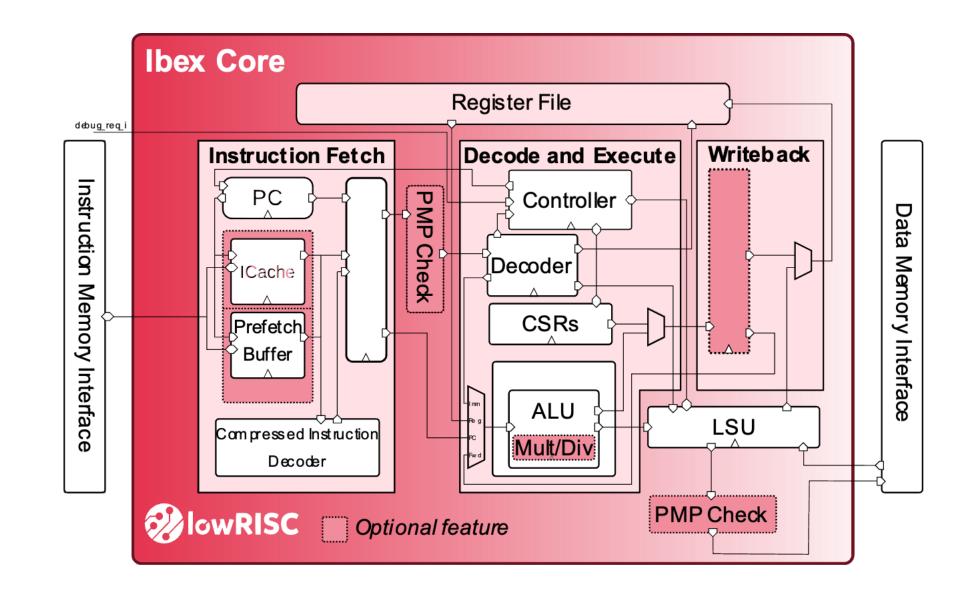

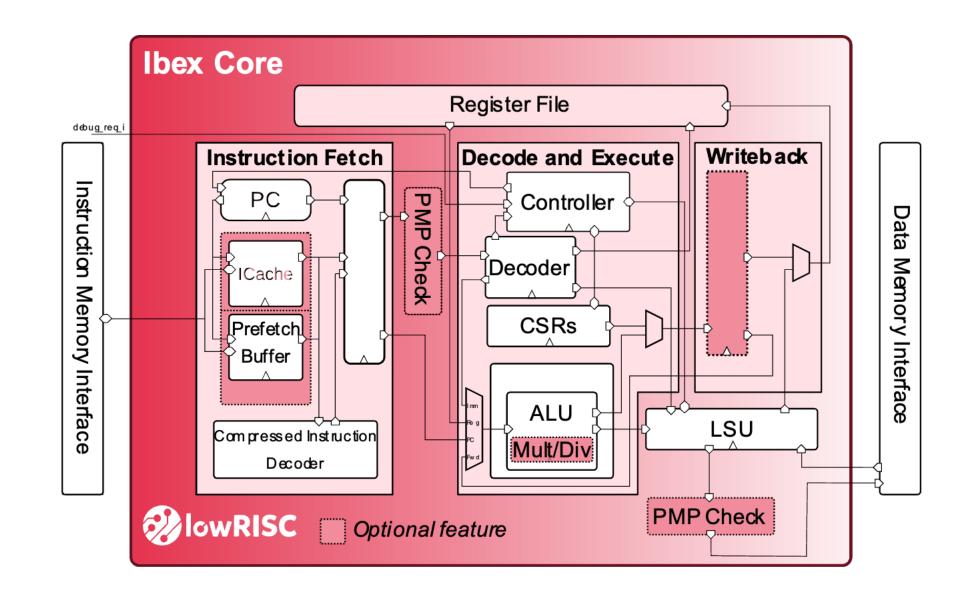

Implemented using Icarus Verilog, Google OR-Tools, and RISC-V Formal Interface

### **Experimental Evaluation**

Implemented using Icarus Verilog, Google OR-Tools, and RISC-V Formal Interface

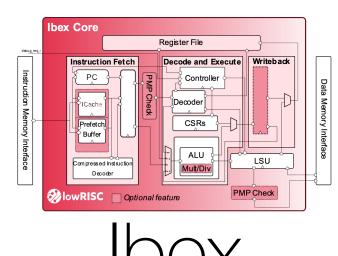

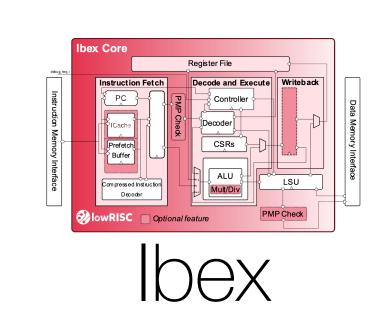

"**Ibex** is a production-quality opensource 32-bit RISC-V CPU core"

### **Experimental Evaluation**

Implemented using Icarus Verilog, Google OR-Tools, and RISC-V Formal Interface

"**Ibex** is a production-quality opensource 32-bit RISC-V CPU core"

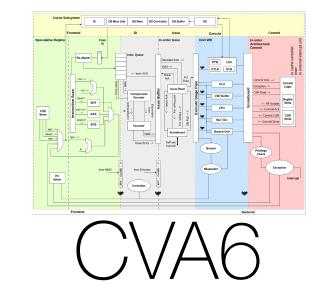

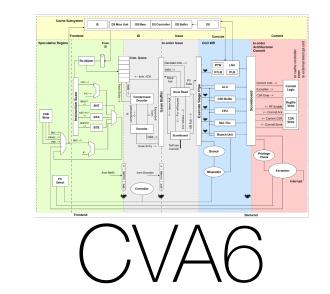

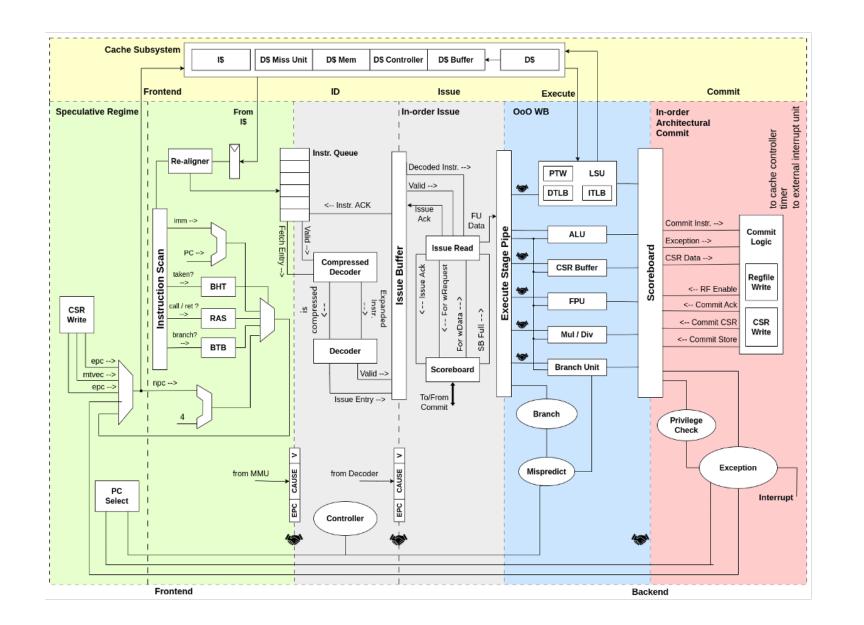

"CVA6 is an application-class 6-stage RISC-V CPU capable of booting Linux"

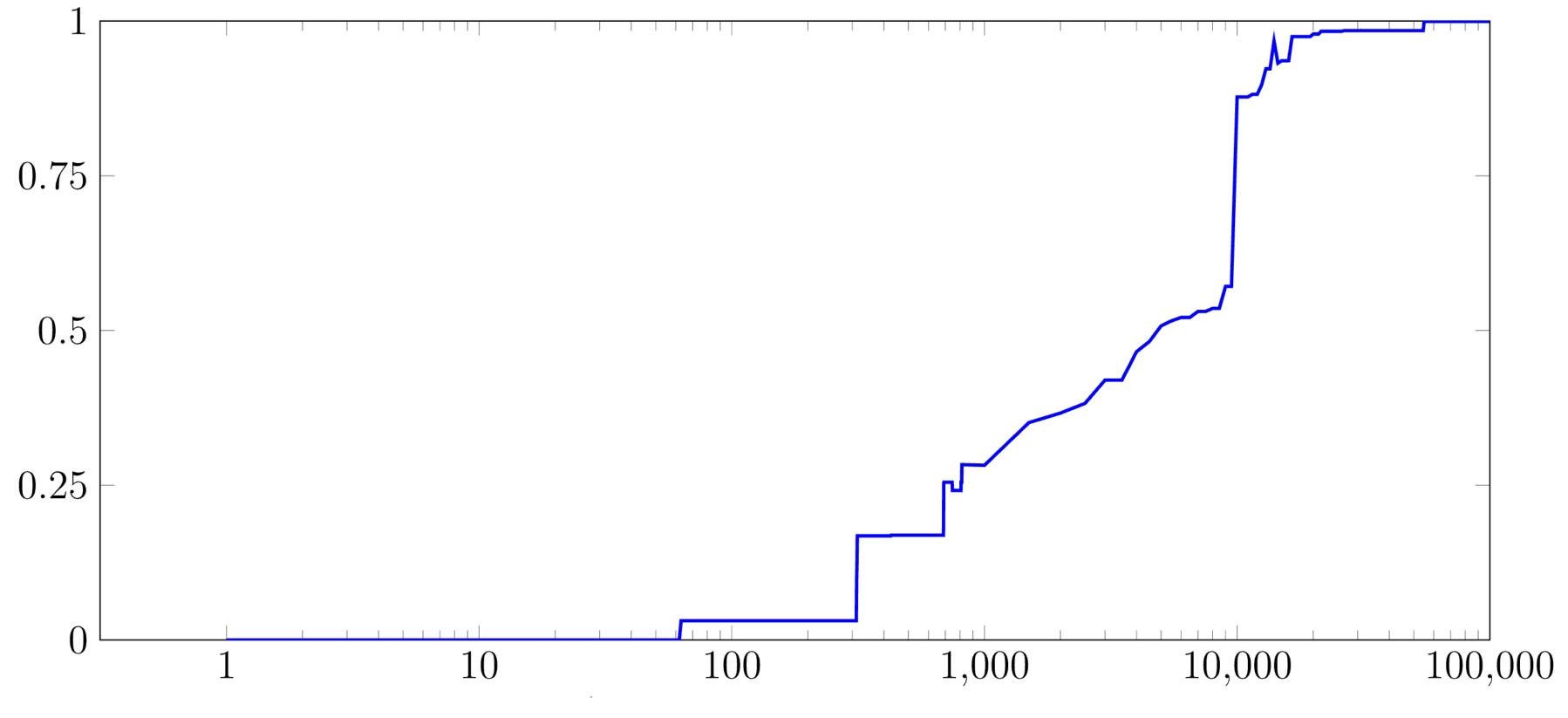

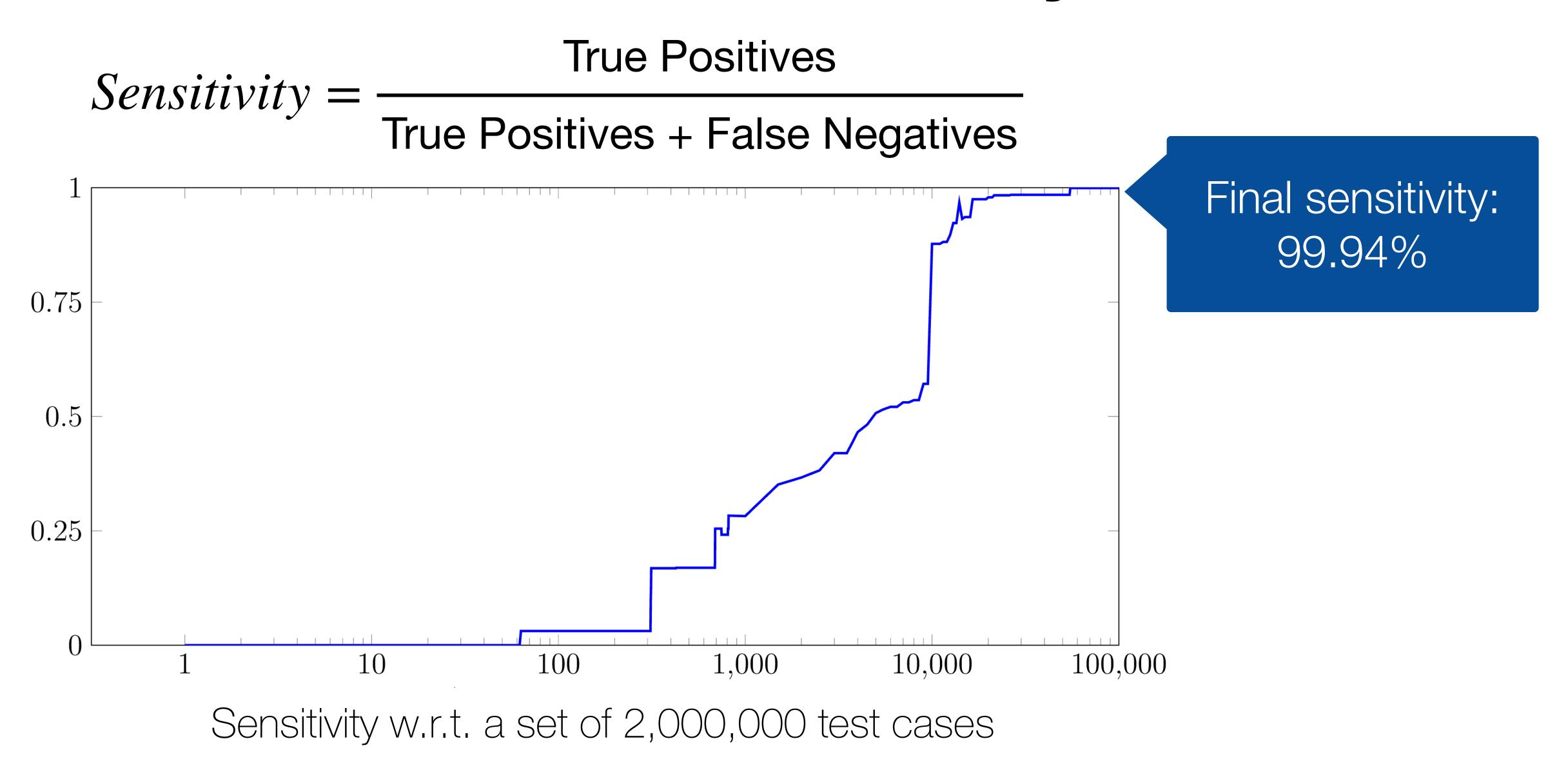

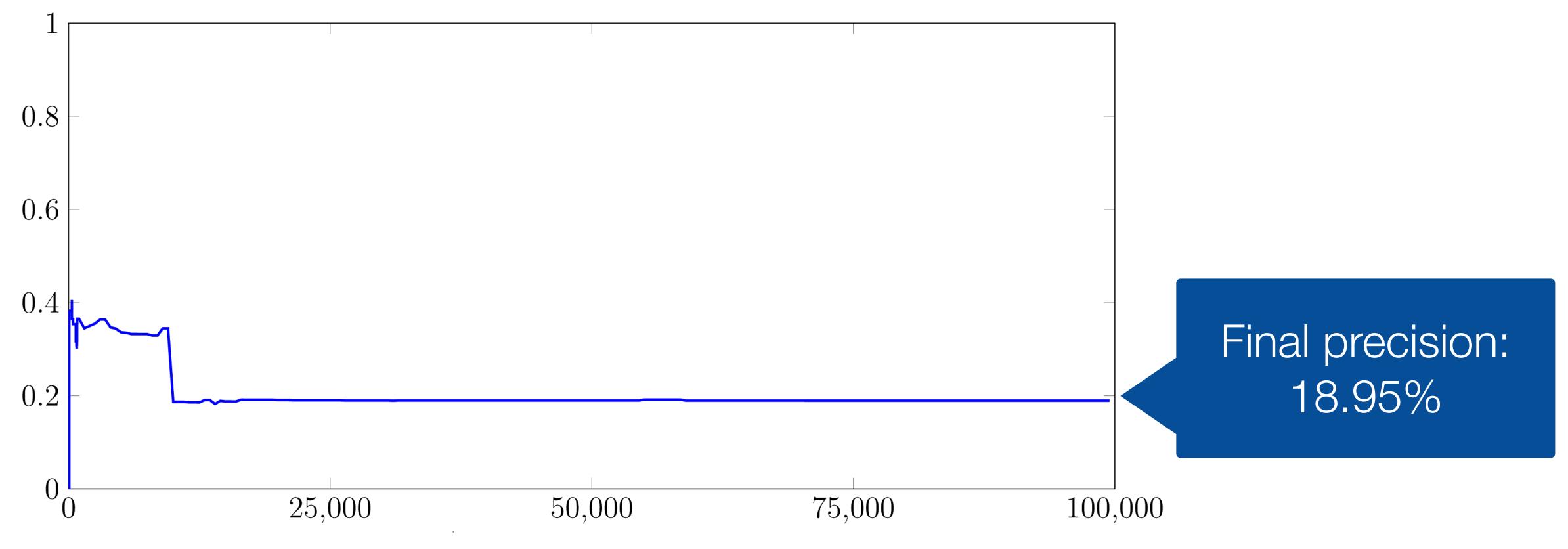

### Performance on Ibex - Sensitivity

$Sensitivity = \frac{\text{True Positives}}{\text{True Positives} + \text{False Negatives}}$

Sensitivity w.r.t. a set of 2,000,000 test cases

### Performance on Ibex - Sensitivity

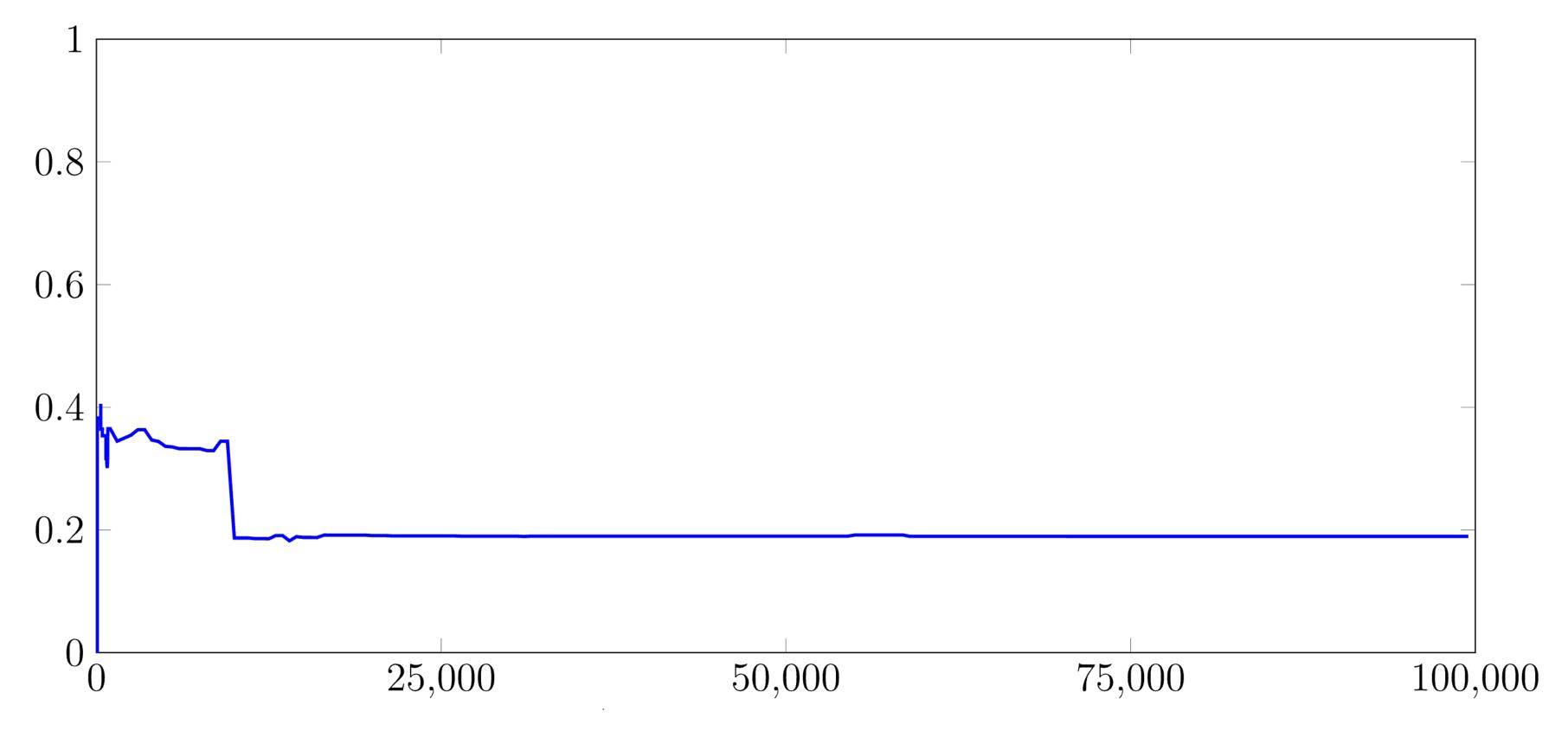

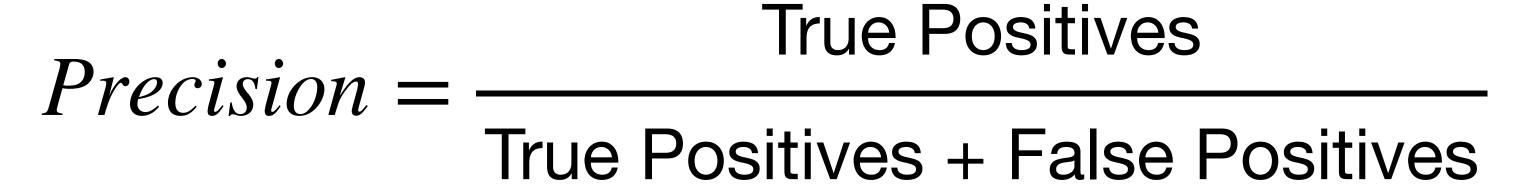

#### Performance on Ibex - Precision

Precision = True Positives

True Positives + False Positives

Precision w.r.t. a set of 2,000,000 test cases

#### Performance on Ibex - Precision

Precision = True Positives

True Positives + False Positives

Precision w.r.t. a set of 2,000,000 test cases

```

li a0, 0 \times 100 a0 \leftarrow 0 \times 100 li a0, 0 \times 102 a0 \leftarrow 0 \times 102 lw a1, 0 \times 100 a1 \leftarrow mem[a0] Program 1

```

```

li a0, 0 \times 100 a0 \leftarrow 0 \times 100 li a0, 0 \times 102 a0 \leftarrow 0 \times 102 lw a1, 0 \times 102 a1 \leftarrow mem[a0] Program 1

```

Slower!

```

li a0, 0 \times 100 a0 \leftarrow 0 \times 100 li a0, 0 \times 102 a0 \leftarrow 0 \times 102

lw a1, 0(a0) a1 \leftarrow mem[a0] lw a1, 0(a0) a1 \leftarrow mem[a0]

```

Program 1

Program 2

Slower!

Address is not aligned

```

li a0, 0 \times 100 a0 \leftarrow 0 \times 100 li a0, 0 \times 102 a0 \leftarrow 0 \times 102

lw a1, 0(a0) a1 \leftarrow mem[a0] lw a1, 0(a0) a1 \leftarrow mem[a0]

Program 1

```

Program 2

Slower!

Address is not aligned

Refinement of template to capture:

- alignment of accessesbranch outcomes

- data dependencies

### Refined Contract Template - Precision

Precision w.r.t. a set of 2,000,000 test cases

# Thank you for your attention!

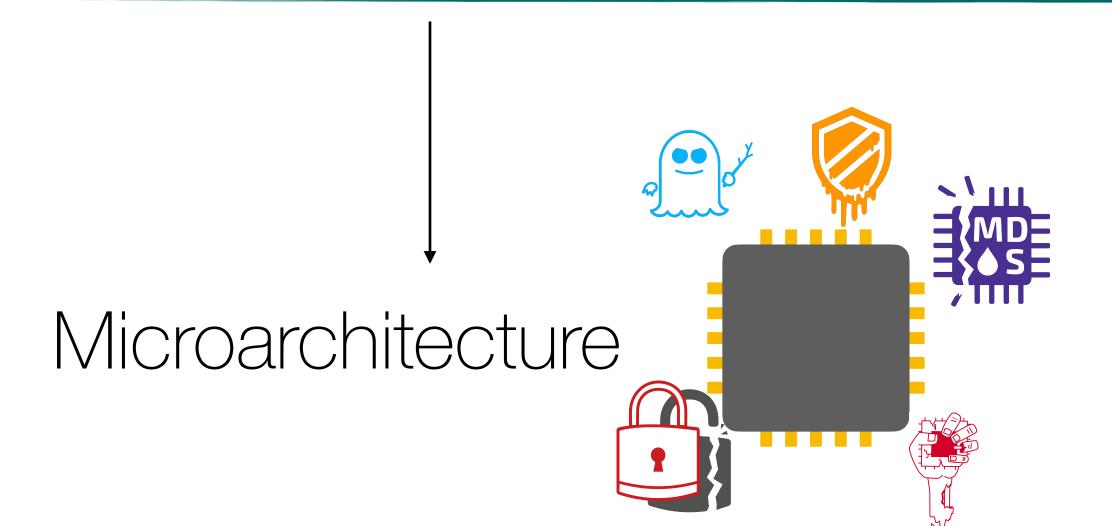

Synthesizing Hardware-Software Leakage Contracts for RISC-V Open-Source Processors Saarland Informatics Campus Marco Guarnieri Saarbrücken, Germany IMDEA Software Institute However, most of today's processor designs lack precise spec-Gideon Mohr ifications of microarchitectural leakage. In this work, we close Saarland University this gap by proposing a semi-automatic methodology for syn-Saarland Informatics Campus thesizing leakage contracts from open-source processor designs. Saarbrücken, Germany Abstract—Microarchitectural attacks compromise security by 1) Definition of Contract Template. A human expert Abstract—Microarchitectural attacks compromise security by exploiting software-visible artifacts of microarchitectural optimizations such as caches and speculative execution. Defending Our methodology consists of four steps: exploiting software-visible armacis of microarchitectural optimizations such as caches and speculative execution. appropriate against such attacks at the software level requires an appropriate determines a set of contract atoms that capture potential instruction-level leakage observations. For example, a mizations such as caches and spectrative execution. Determing against such attacks at the software level requires an appropriate obstruction of the instruction set prohitosture (ICA) level that against such attacks at the software level requires an appropriate abstraction at the instruction set architecture (ISA) level that captures microarchitectural leakage Hardware-coftware leakage atom may expose the value of the register operand of a memory abstraction at the instruction set architecture (15A) level that captures microarchitectural leakage. Hardware-software leakage captures have recently been proposed as such an abstraction. instruction. The set of all contract atoms forms the contract captures microarcimectural leakage. Haruware-sumware leaka contracts have recently been proposed as such an abstraction. In this paper, we propose a semi-automatic methodology for template, and any of its subsets is a candidate contract. In this paper, we propose a semi-automatic methodology for synthesizing hardware-software leakage contracts for open-source microarchitectures. For a given ISA, our approach relies on human 2) Test-Case Generation. A human expert devises a test-case synthesizing nardware-software leakage contracts for open-source microarchitectures. For a given ISA, our approach relies on human experts to (a) continue the space of noceible contracts in the form generation strategy. Each test case consists of two ISA-level microarcinectures, ror a given 15A, our approach renes on numan experts to (a) capture the space of possible contracts in the form of contract templates and (b) device a test-case generation etratem. programs with fixed data inputs. These test cases are used to experts to (a) capture the space of possible contracts in the form of contract templates and (b) devise a test-case generation strategy exercise and analyze a processor's microarchitectural leakage. or contract templates and (b) devise a test-case generation strategy to explore a microarchitecture's potential leakage. For a given implementation of an ICA those two ingredients are then used to 3) Evaluation of Test Cases. Test cases are automatically whore a microarchitecture's potential leakage, for a given mentation of an ISA, these two ingredients are then used to implementation of an ISA, these two ingredients are then used to automatically synthesize the most precise leakage contract that is satisfied by the microarchitecture evaluated on the target processor design to determine which test cases are distinguishable, i.e., lead to distinguishable executions sausned by the microarchitecture.

We have instantiated this methodology for the RISC-V ISA for a given microarchitectural attacker. Distinguishable test cases We have instantiated this methodology for the KISC-V ISA and applied it to the Ibex and CVA6 open-source processors.

Our experimente demonstrate the practical applicability of the expose actual leaks that need to be accounted for at contract and applied it to the libex and UVA6 open-source processors.

Our experiments demonstrate the practical applicability of the methodology and uncover subtle and unexpected looks level. Test cases are also automatically evaluated on the contract promise the security of programs by exploiting software-visible artifacts of microarchitectural optimizations such as caches and speculative execution. Defending against such attacks in software speculative execution. Defending against such attacks in software attacks in software speculative execution. Our experiments demonstrate the practical applicability methodology and uncover subtle and unexpected leaks. artifacts of microarchitectural optimizations such as caches and speculative execution. Defending against such attacks in software is challenging, instruction set architectures (ISAs), the traditional is challenging, instruction set architectures (ISAs). exposing the value of register operands for memory instructions 4) Automatic Contract Synthesis. Based on the results of the test-case evaluation, a contract, i.e. a set of contract atoms, is automatically synthesized from the distinguishing atoms speculative execution. Detenuing against such attacks in software is challenging: instruction set architectures (ISAs), the traditional contracts) have recently been proposed as a new security abstraction at the ISA level to fill this gap. Such contracts aim to capture associated with attacker-distinguishable test case. Our approach is automatically synthesized from the distinguishing atoms is automatically synthesized from the distinguishing atoms is automatically synthesized from the distinguishing atoms automatically synthesized from the distinguishing atoms is automatically synthesized from the distinguishing atoms at the ISA level to fill this gap. Such contracts aim to capture associated with attacker-distinguishable test case. Our approach is automatically synthesized contract is satisfied by the processor associated with attacker-distinguishable test case. is chancinging, instruction set architectures (15As), the traditional hardware-software interface, abstract from microarchitectural details and thus do not give any guarantees W.r.t. these attacks. design on all test cases, i.e., it captures all leaks exposed by leakage traces, i.e., sequences of leakage observations, with ISA-level executions. For example, a contract could expose the ISA-level executions. For example, a contract could expose the observations to the example of memory inetractions as leakage observations to the example of memory inetractions as leakage observations to the example of memory inetractions as leakage observations to the example of memory inetractions as leakage observations to the example of memory inetractions as leakage observations to the example of memory inetractions as leakage observations to the example of memory inetractions as leakage observations to the example of memory inetractions as leakage observations to the example of memory inetractions as leakage observations to the example of memory inetractions as leakage observations to the example of memory inetractions as leakage observations to the example of memory inetractions are leakage observations to the example of memory inetractions are leakage observations. ISA-level executions. For example, a contract could expose the the test cases on the processor. Moreover, it also ensures that the test cases on the processor. Moreover, it also ensures that the test cases on the processor. Moreover, it also ensures that the test cases on the processor. Moreover, it also ensures that the test cases on the processor. Moreover, it also ensures that the test cases on the processor. Moreover, it also ensures that the test cases on the processor. Moreover, it also ensures that the test cases on the processor. Moreover, it also ensures that the test cases on the processor. Moreover, it also ensures that the test cases on the processor. Moreover, it also ensures that the test cases on the processor. Moreover, it also ensures that the test cases on the processor and the test cases on the processor. Moreover, it also ensures that the test cases on the processor and the test cases of the test memory instructions as leakage observations to the synthesized contract is the most precise such contract, i.e., the synthesized contract is the most precise such contract, i.e., the synthesized contract is the most precise such contract, i.e., the synthesized contract is the most precise such contract, i.e., the synthesized contract is the most precise such contract, i.e., the synthesized contract is the most precise such contract, i.e., the synthesized contract is the most precise such contract, i.e., the synthesized contract is the most precise such contract, i.e., the synthesized contract is the most precise such contract, i.e., the synthesized contract is the most precise such contract. tion at the 15A level to mi uns gap. Such contracts and to capture possible microarchitectural side-channel leaks by associating The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The proliferation of the open-source KISC-V ISA LIST and The open-source KISC-V ISA LIST and

Read the paper (to appear at DATE 2024): <a href="https://arxiv.org/abs/2401.09383">https://arxiv.org/abs/2401.09383</a>

Play with the artifact:

https://github.com/hw-sw-contracts/riscv-

contract-synthesis

https://zenodo.org/records/10491534