### Hardware-Software Contracts for Secure Speculation

Joint work with Marco Guarnieri, Pepe Vila @ IMDEA Software, Madrid Boris Köpf @ Microsoft Research, Cambridge, UK

Supported by the European Research Council and an Intel Strategic Research Alliance (ISRA)

### The Need for HW/SW Contracts

### **ISA: Benefits**

### High-level language

### Instruction set architecture (ISA)

### Microarchitecture

### Can program independently of microarchitecture

### Can implement **arbitrary** optimizations as long as ISA semantics are obeyed

### Inadequacy of the ISA: Side channels

### High-level language

### Instruction set architecture (ISA)

Impossible to program securely cryptographic algorithms? sandboxing untrusted code?

### **No guarantees** about side channels

Can implement arbitrary insecure optimizations as long as ISA is implemented correctly

### **A Way Forward: HW/SW Security Contracts**

### Can program **securely** on top of contract independently of microarchitecture

### HW/SW contract = ISA + X

as long as contract is obeyed

### **Succinctly captures possible information leakage**

### Can implement arbitrary insecure optimizations

A Concrete Challenge: Spectre

### Exploits *speculative* execution

### Almost *all* modern *CPUs* are affected

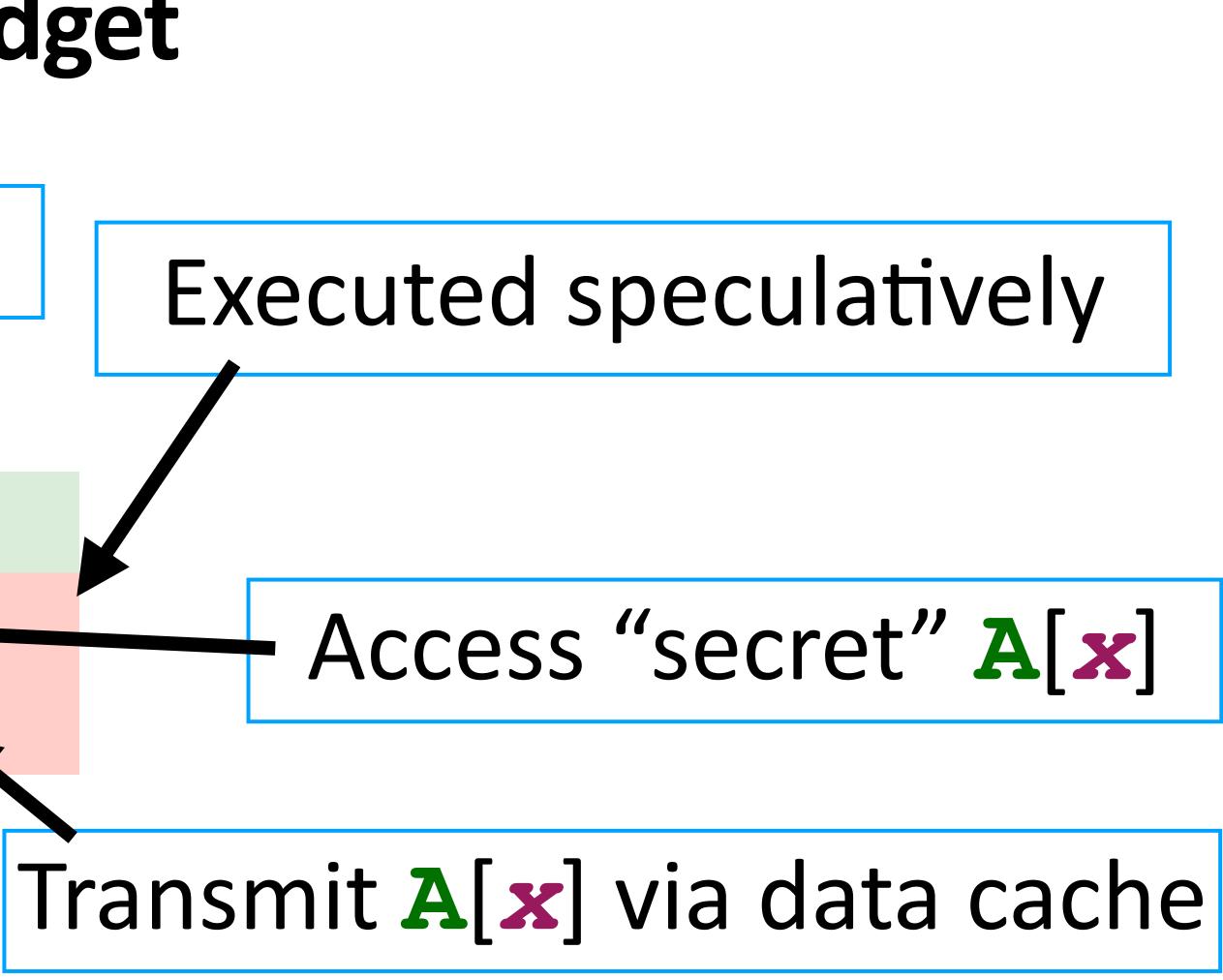

### **Example:** Spectre v1 Gadget

# x is out of bounds . . if (x < A\_size) . . y = A[x] . . z = B[y\*512] . . end</pre>

### NDA: Preventing Speculative Execution Attacks at Their Source Hardware Countermeasures InvisiSpec: Making Speculative F Mengjia Yan<sup>†</sup>, Jiho Choi<sup>†</sup>, Dimitrios Skarlatos, Adr {myan8, jchoi42, skarlat2}@`` University of Michigan University of Michigan stefanos.kaxiras@it.uu.se CleanupSpec: An "Undo" Approach to Safe Speculation Gururaj Saileshwar Moinuddin K. Qureshi Moinuddin K. Qureshi rean **Speculative Taint Tracking (STT): A Comprehensive Protection** for Speculatively Accessed Data Mengjia Yan Artem Khyzha Tel Aviv University University of Illinois at artkhyzha@mail.tau.ac.il Urbana-Champaign Georgia Institute of Teck myan8@illinois.edu

Josep Torrellas

Christopher W. Fletcher

### Examples

# if (x < A size)</li> y = A[x] z = B[y\*512] end

Delay loads until they can be retired [Sakalis et al., ISCA'19]

### Delay loads until they cannot be squashed [Sakalis et al., ISCA'19]

Taint speculatively loaded data + delay tainted loads [STT and NDA, MICRO'19]

### Examples

# y = A[x] if (x < A size)</li> z = B[y\*512] end

Delay loads until they can be retired [Sakalis et al., ISCA'19]

### Delay loads until they cannot be squashed [Sakalis et al., ISCA'19]

Taint speculatively loaded data + delay tainted loads [STT and NDA, MICRO'19]

What security properties do HW countermeasures enforce?

How can we program securely?

### A Proof of Concept

### M. Guarnieri, B. Köpf, J. Reineke, and P. Vila Hardware–Software Contracts for Secure Speculation S&P (Oakland) 2021

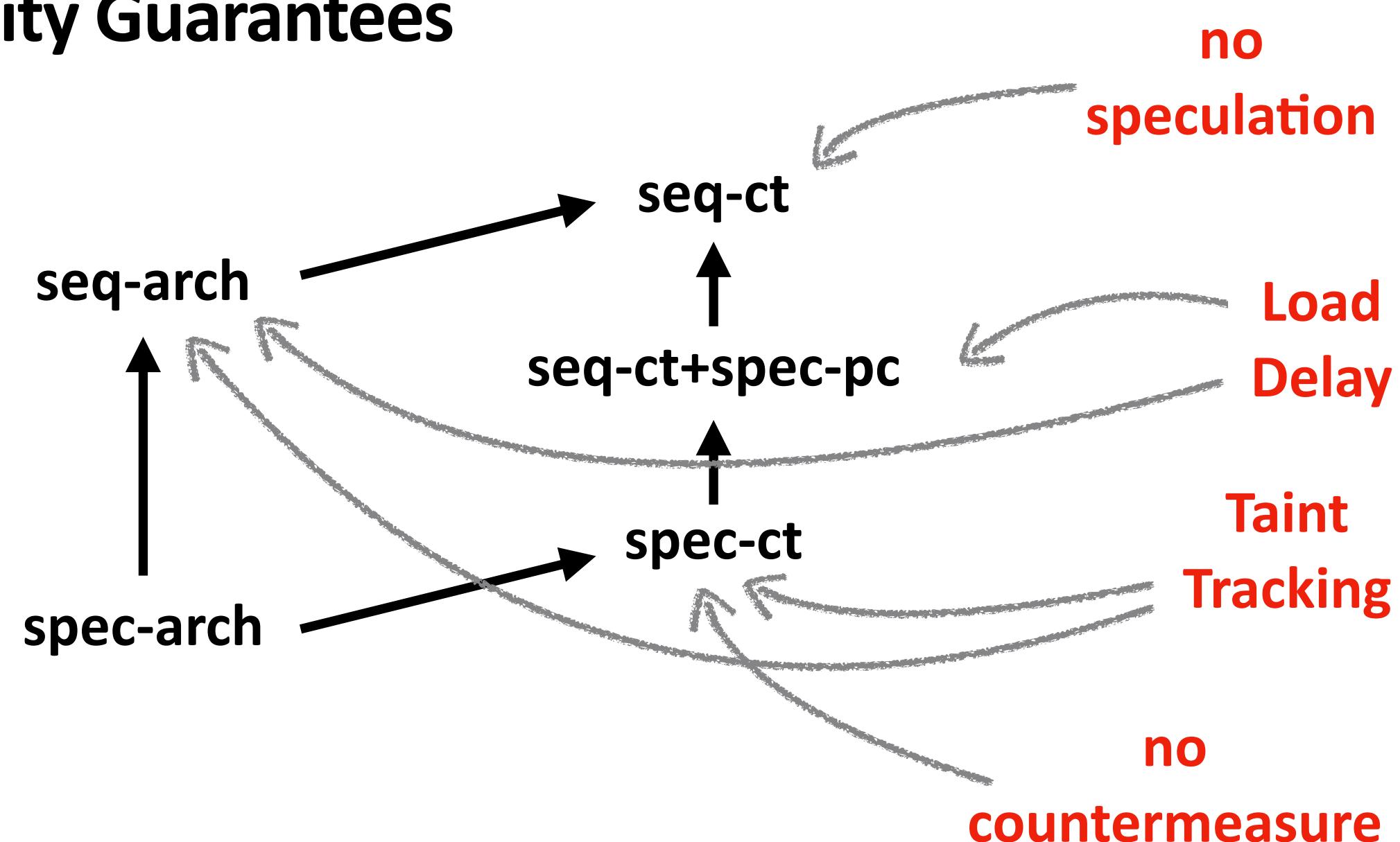

### Hardware-Software Contracts

### **HW/SW Contracts for Secure Speculation**

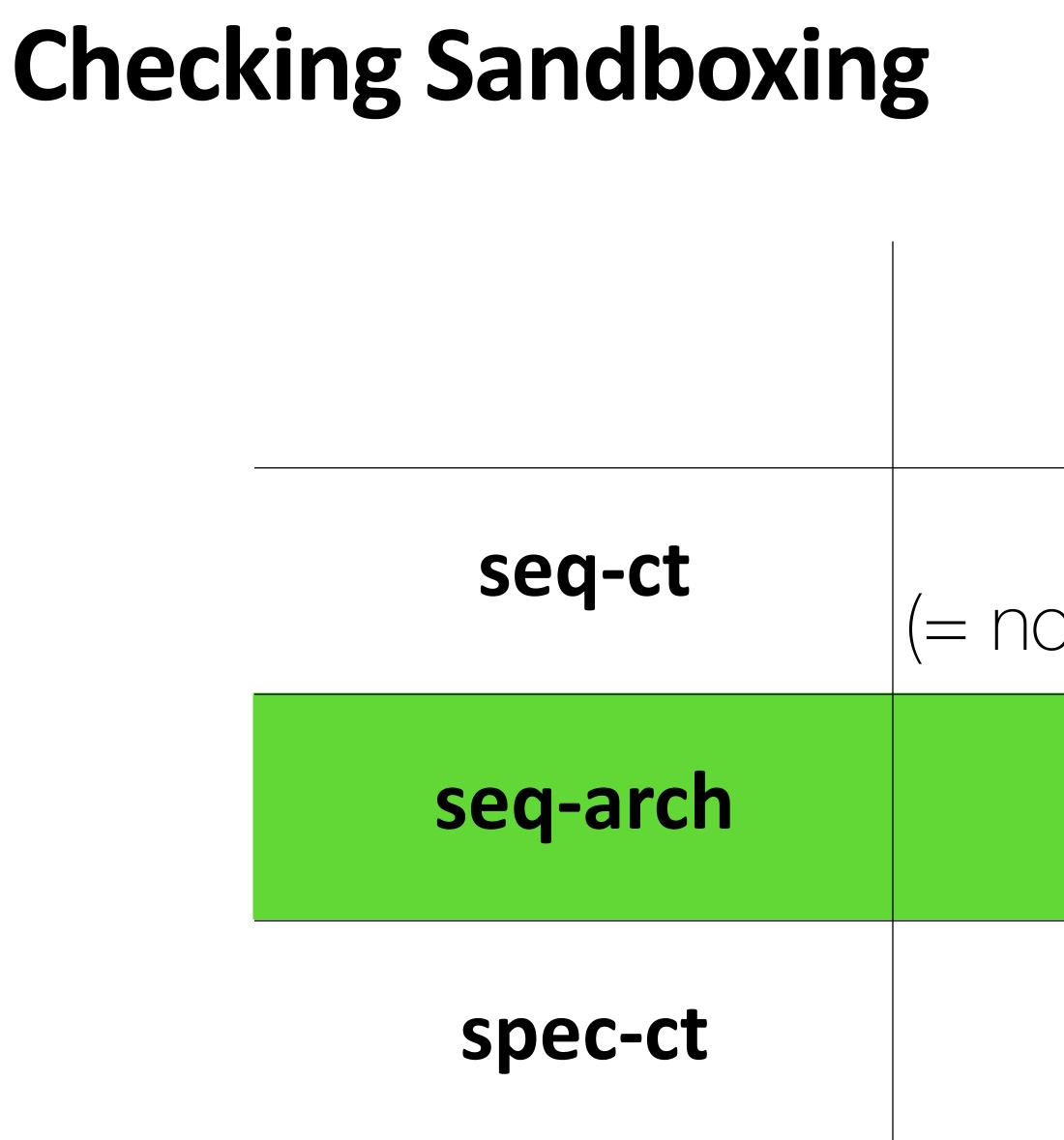

Secure Programming

### HW/SW Contracts for Secure Speculation

Hardware Countermeasures

Load Delay

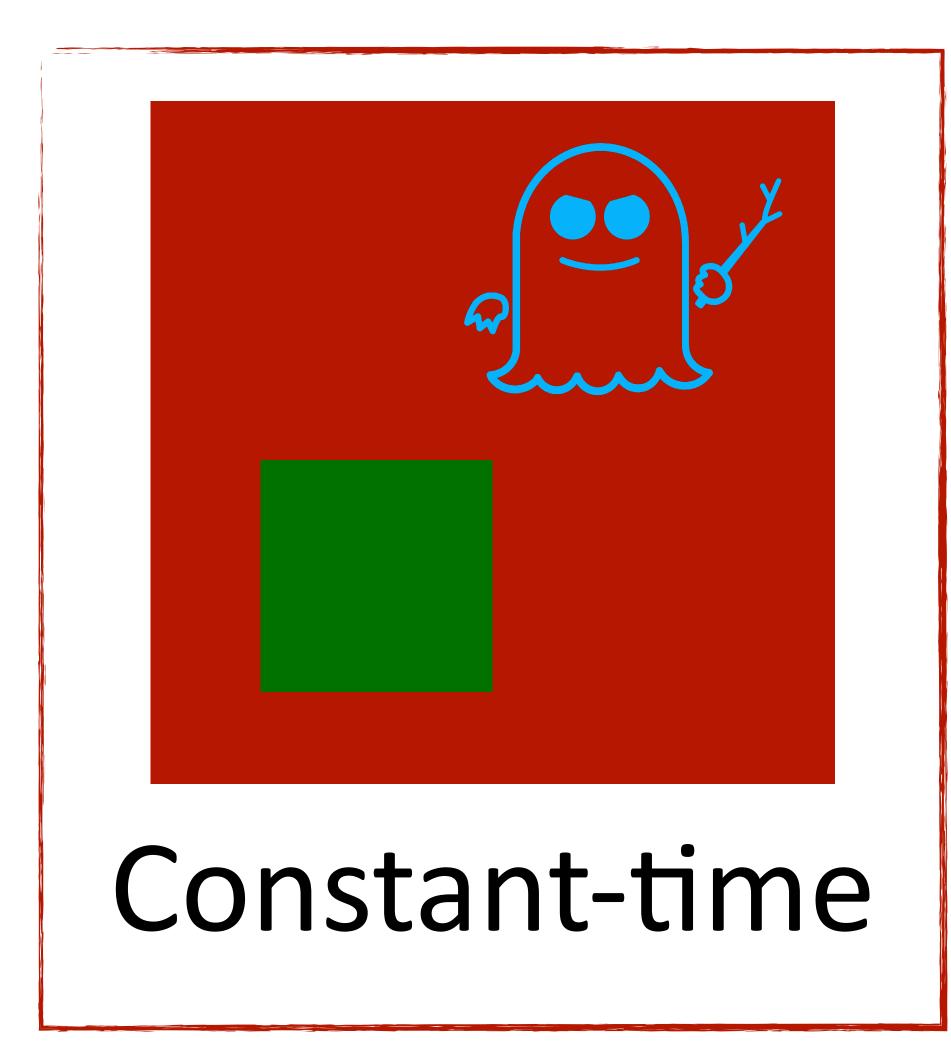

Constant-time

Sandboxing

### mechanism-independent simple Desiderata: at "ISA level" precise

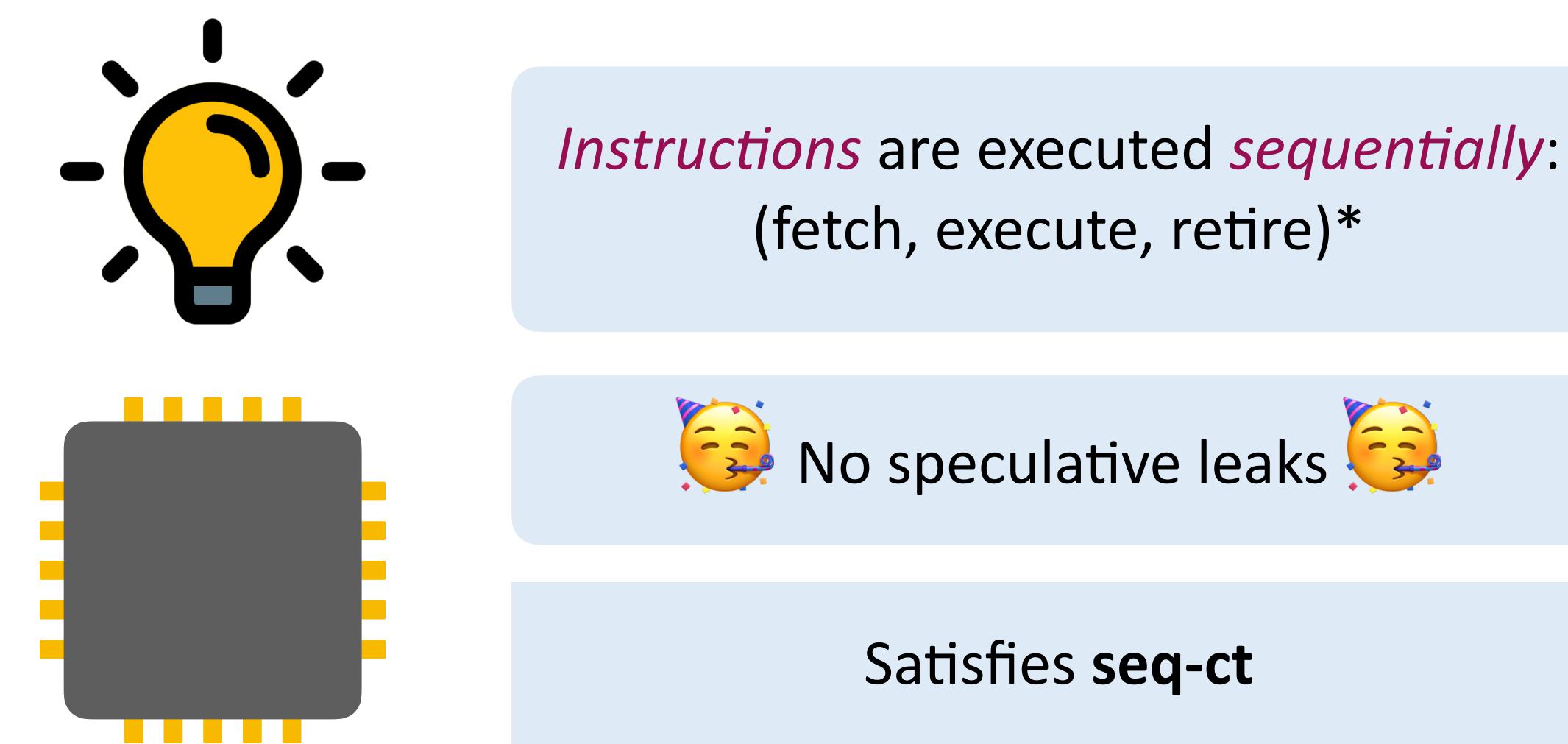

### No speculation

**Taint Tracking**

No countermeasures

### **HW/SW Contracts for Secure Speculation**

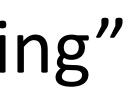

### **Contracts** specify which **program executions** a side-channel adversary cannot distinguish

### Contract traces: $[\mathbb{E}](p, \sigma)$

### "What leaks" about an execution

### Contracts

### Attacker observes sequences of *µarch states*

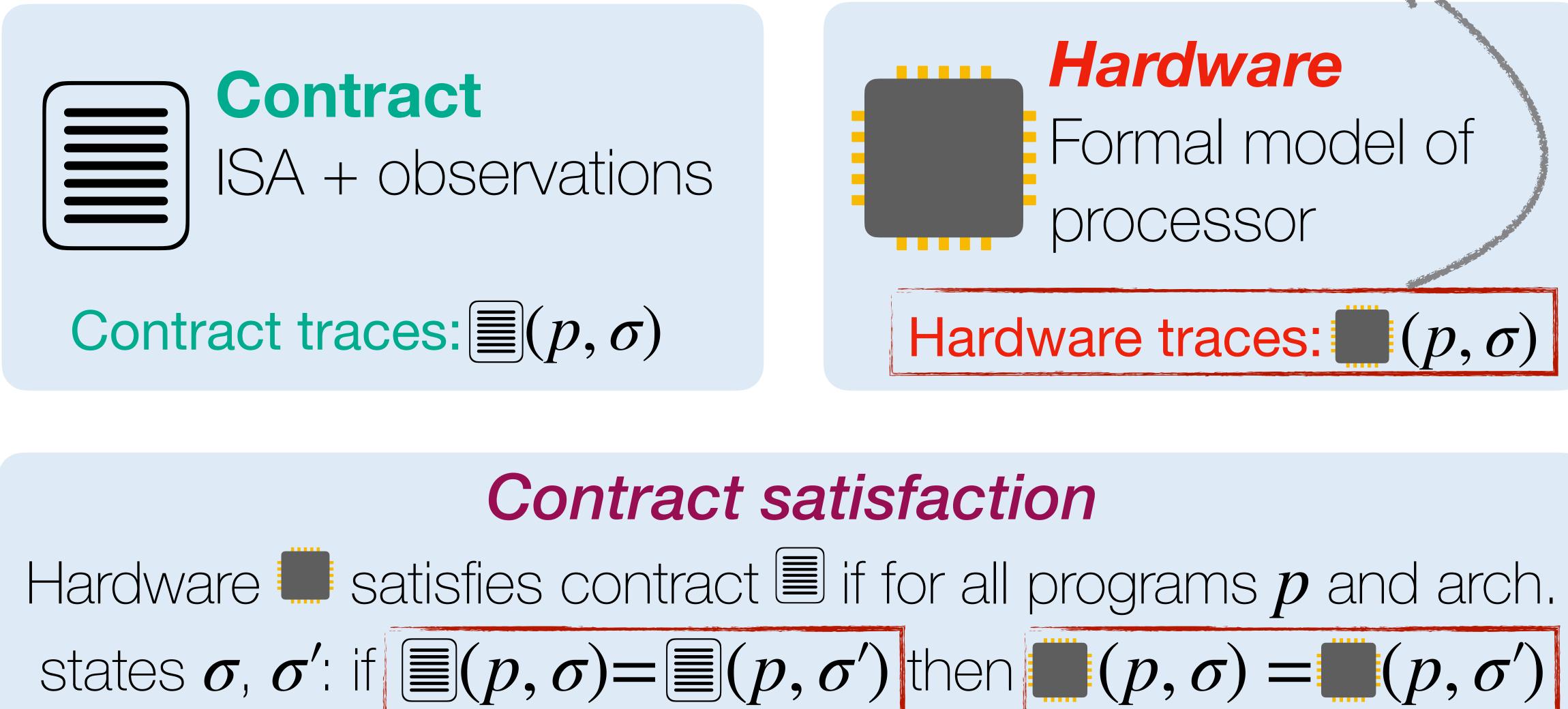

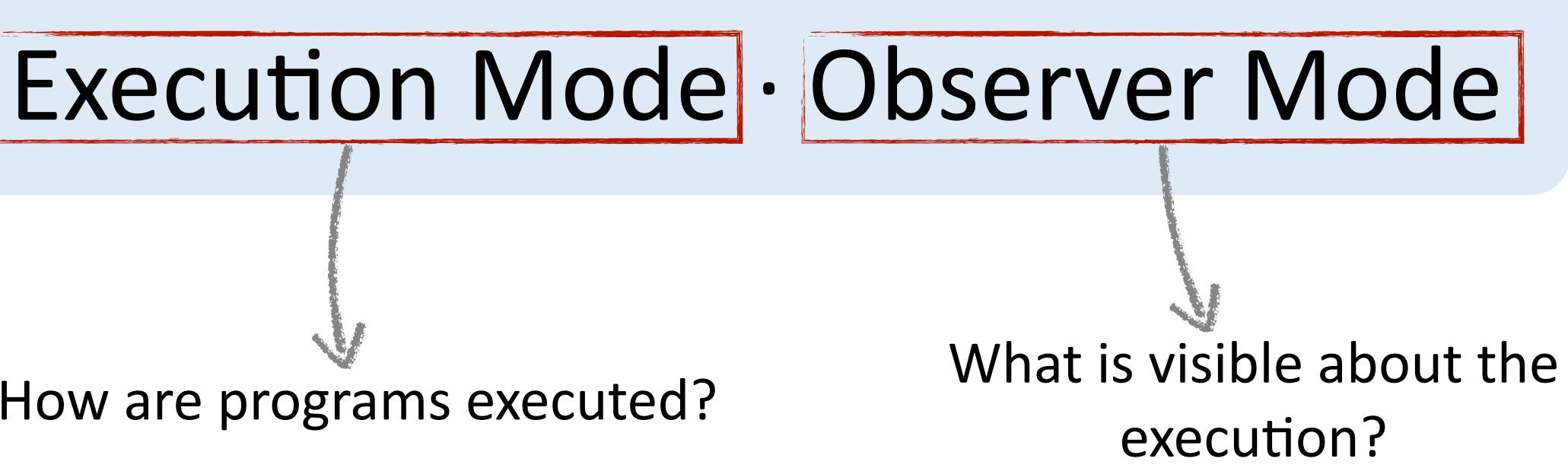

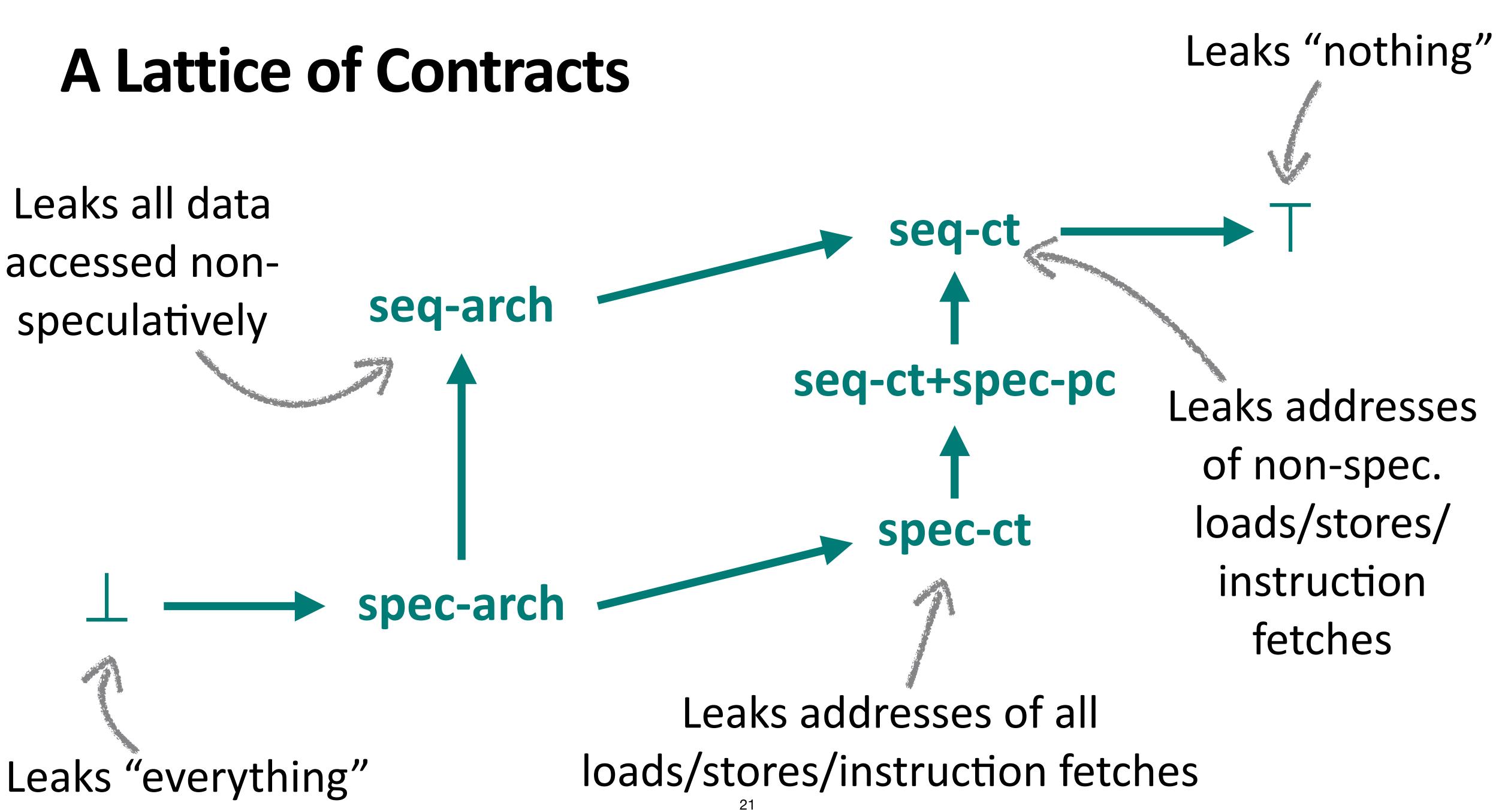

### **Contracts for Secure Speculation**

# **Contract =**

How are programs executed?

### **Contracts for Secure Speculation**

### **Contract = Execution Mode · Observer Mode**

seq — sequential execution **spec** — mispredict branch instructions

### **Contracts for Secure Speculation**

### **Contract = Execution Mode · Observer Mode**

### pc — only program counter

ct — pc + addr. of loads and stores

arch — ct + loaded values

### Example: seq-ct

### 1. if (x < A size) 2. $y = \mathbf{A}[\mathbf{x}]$ $\boldsymbol{z} = \boldsymbol{B}[\boldsymbol{y}]$ 3. end 4.

### Assume x < A size

22

35

### Example: seq-arch

### 1. if (x < A size)2. $\mathbf{y} = \mathbf{A}[\mathbf{x}]$ $\boldsymbol{z} = \boldsymbol{B}[\boldsymbol{y}]$ 3. end 4.

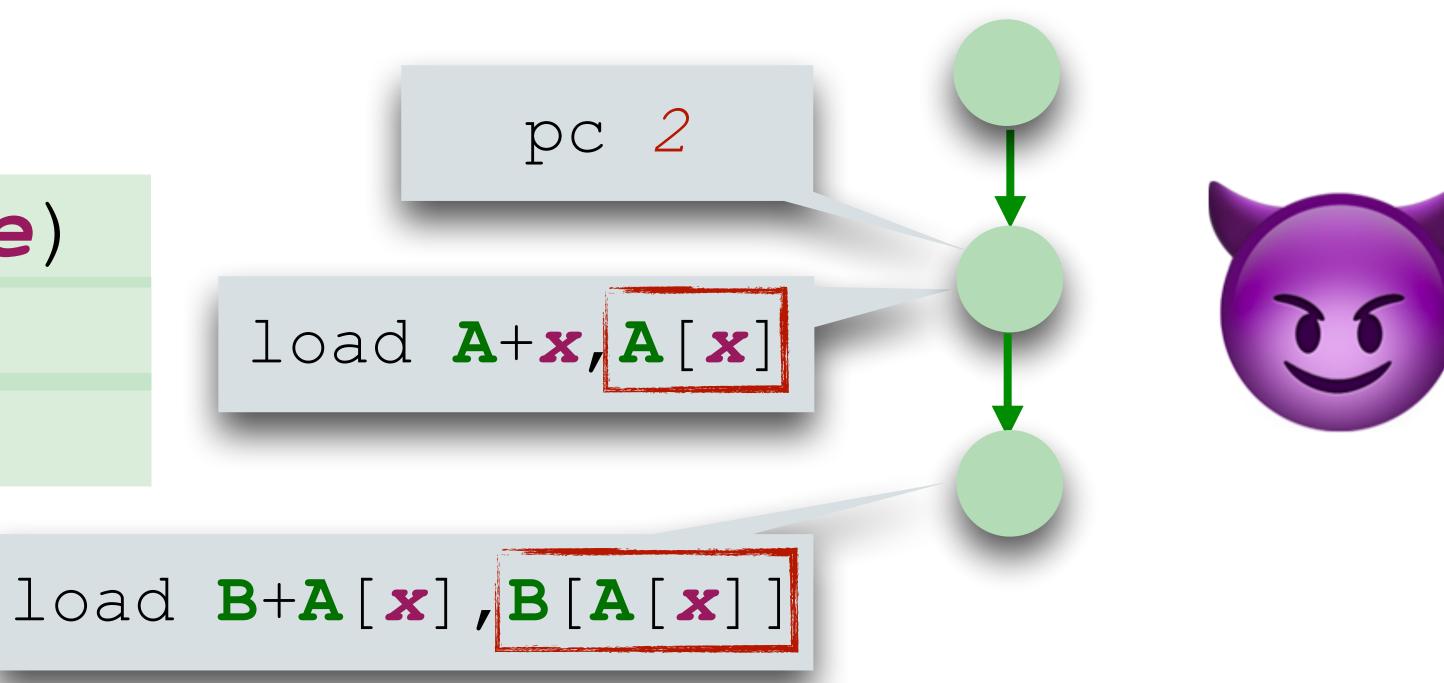

### Example: spec-ct

1. if  $(\mathbf{x} < \mathbf{A} \ size)$ 2.  $\mathbf{y} = \mathbf{A}[\mathbf{x}]$ z = B[y]3. end 4.

### Assume x > A size

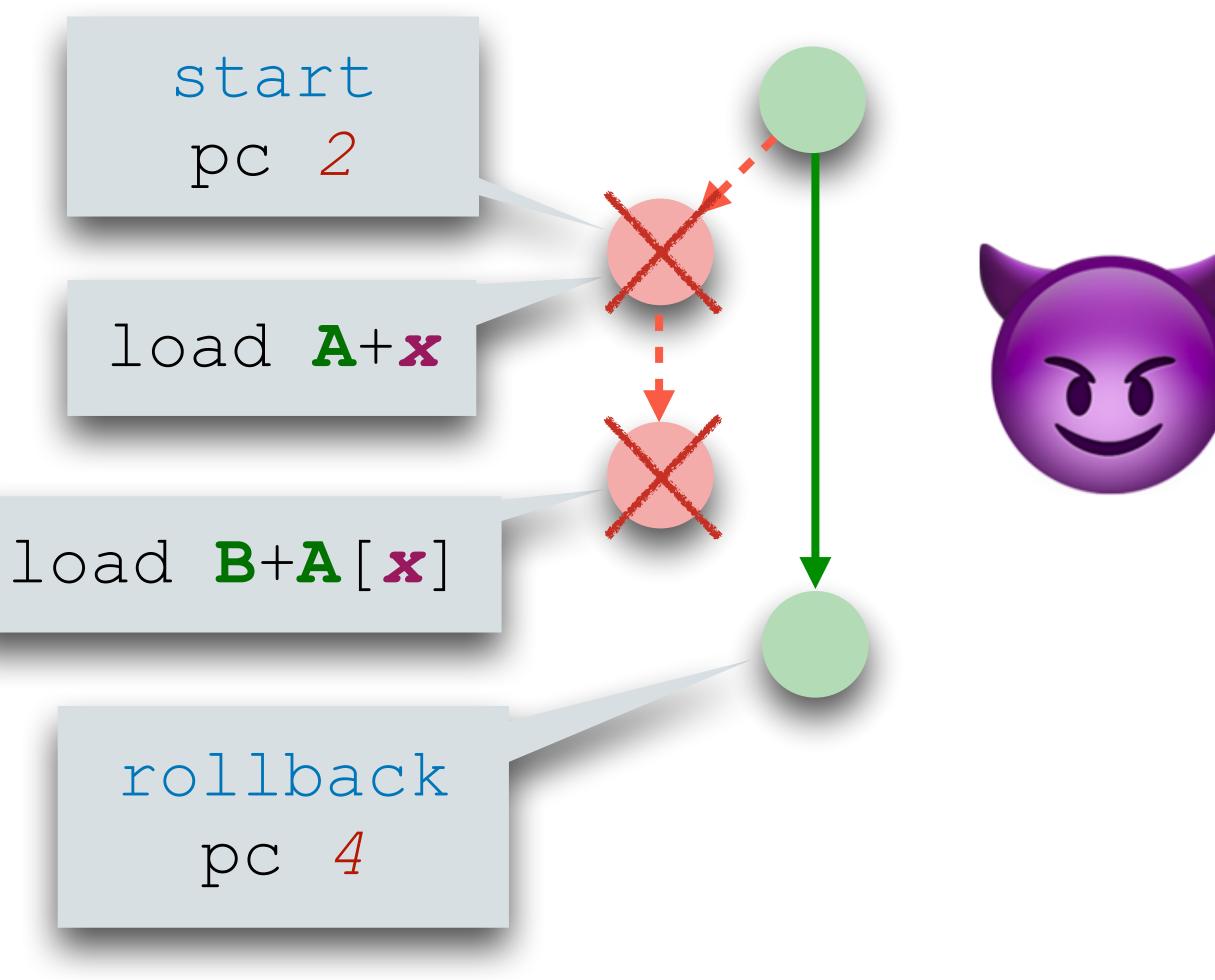

### Hardware Countermeasures

### **A Simple Processor**

### *3-stage pipeline* (fetch, execute, retire)

Speculative and out-of-order execution

Parametric in *branch predictor* and *memory hierarchy*

Different *schedulers* for different countermeasures

### **Disabling Speculative Execution**

### Security guarantees?

# if (x < A\_size) z = A[x] y = B[z]</pre>

# A[x] and B[z] delayed until x < A size is resolved</pre>

# z = A[x] if (x < A\_size) y = B[z]</pre>

## B[z] delayed until x < A size is resolved</pre>

# z = A[x] if (x < A size) if (z==0) skip</pre>

### Observation: Can only leak data accessed non-speculatively

### if (z==0) is not delayed

### Program speculatively leaks **A**[**x**]

Satisfies seq-arch

Satisfies seq-ct+spec-pc

### Taint Tracking [Yu et al. 2019, Weisse et al. 2019]

### Taint speculatively loaded data

### Security guarantees?

### **Delay** tainted operations

### Taint Tracking [Yu et al. 2019, Weisse et al. 2019]

### if (x < A\_size) z = A[x] y = B[z]

A [x] tainted as unsafe

B [z] delayed until

A [x] is safe

### Taint Tracking [Yu et al. 2019, Weisse et al. 2019]

# z = A[x] if (x < A size) y = B[z]</pre>

### Also satisfies seq-arch

# A [ x ] tagged as safe B [ z ] not delayed

### Program speculatively leaks **A**[**x**]

### No Countermeasure [The World until 2018]

# if (x < A\_size) z = A[x] y = B[z]</pre>

### Leaks addressed of speculative and non-speculative accesses

### Satisfies spec-ct

### **Security Guarantees**

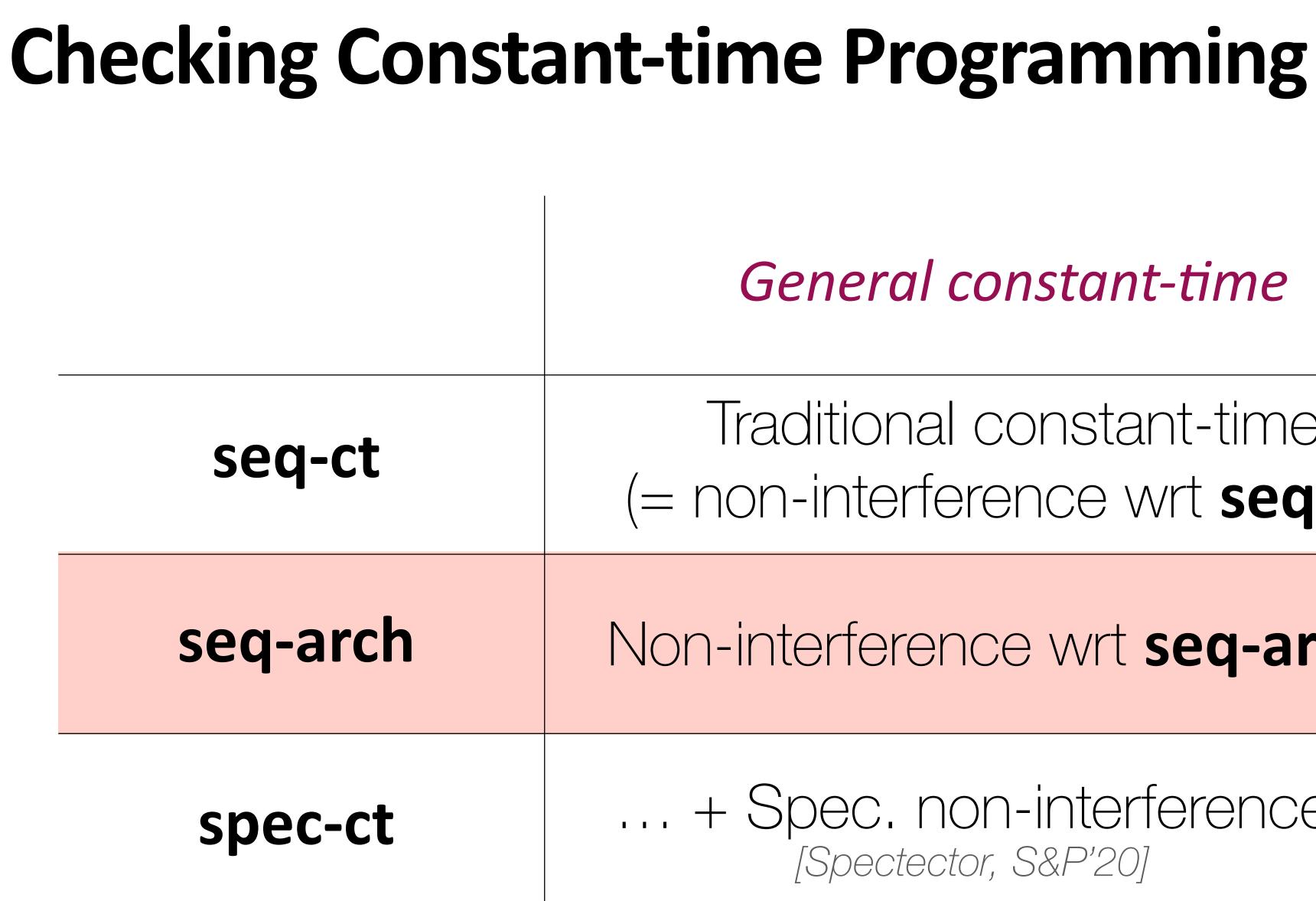

# Secure Programming

# **Two Flavors of Secure Programming**

# Constant-time

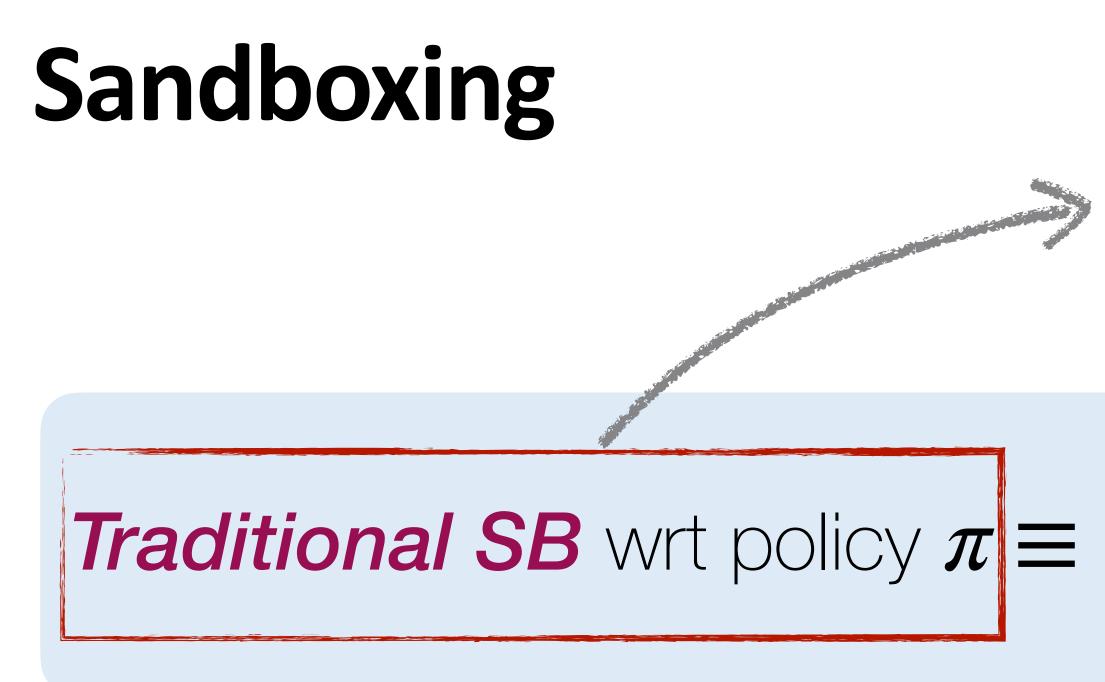

# Sandboxing

# **Two Flavors of Secure Programming**

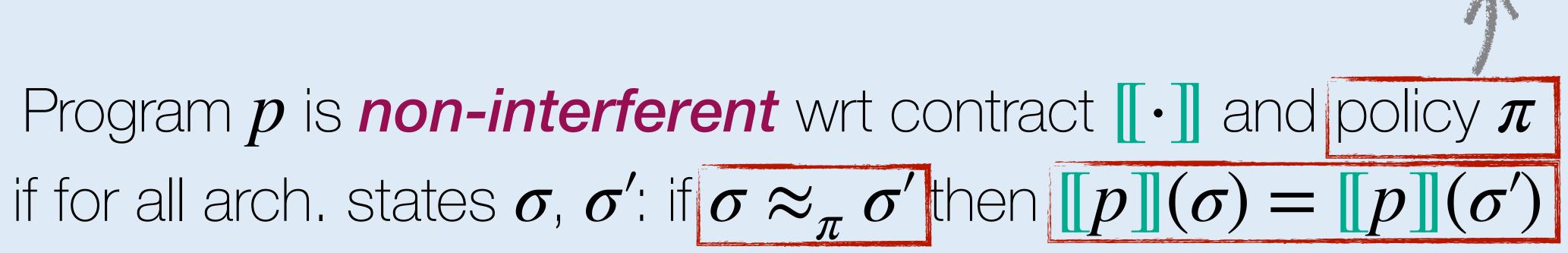

## **Secure Programming: Foundations**

#### Theorem

#### Specify secret data

## If p is **non-interferent** wrt contract $|\cdot|$ and policy $\pi$ , and hardware { • } satisfies [ • ], then p is **non-interferent** wrt hardware $\{\cdot\}$ and policy $\pi$ .

## **General SB** wrt $\pi$ and $\llbracket \cdot \rrbracket \equiv$ Traditional SB wrt $\pi$ + non-interference wrt $\pi$ and $\llbracket \cdot \rrbracket$

# Programs **never access** secret memory locations (out-of-sandbox)

#### *Traditional SB* wrt policy $\pi \equiv$ non-interference wrt seq-arch and $\pi$

#### General sandboxing

# Traditional sandboxing (= non-interference wrt **seq-arch**)

Traditional sandboxing

#### ... + weak SNI

# **Constant-time Programming**

#### Control flow and memory accesses do not depend on secrets

#### *Traditional CT* wrt policy $\pi \equiv$ non-interference wrt seq-ct and $\pi$

### **General CT** wrt $\pi$ and $|\cdot| \equiv$ non-interference wrt $|\cdot|$ and $\pi$

#### General constant-time

#### Traditional constant-time (= non-interference wrt **seq-ct**)

Non-interference wrt seq-arch

#### No access to secrets!

... + Spec. non-interference [Spectector, S&P'20]

# Work in progress: Contracts meet "the real world"

# **Contracts for Real ISAs + Real CPUs**

3-stage pipeline

#### **Microarchitecture**

Register transfer level designs

Manual proof

Toy ISA (6 instr.) + observer modes

Contract

Automatic proof

Real ISA + observer modes

# **Contracts for Real ISAs + Real CPUs**

#### **Microarchitecture**

#### Register transfer level designs

Open-source **RISC-V** cores

SMT solvers + Invariant inference

#### Contract

Automatic proof

#### Real ISA + observer modes

Separate ISA from observer mode

# Separating Observer from ISA satisfaction

# Hardware satisfies contract if for all programs p and arch. states $\sigma$ , $\sigma'$ : if $\equiv (p, \sigma) = \equiv (p, \sigma')$ then $\equiv (p, \sigma) = \equiv (p, \sigma')$

### **ISA** satisfaction

### **Contract satisfaction**

## **Observer** satisfaction

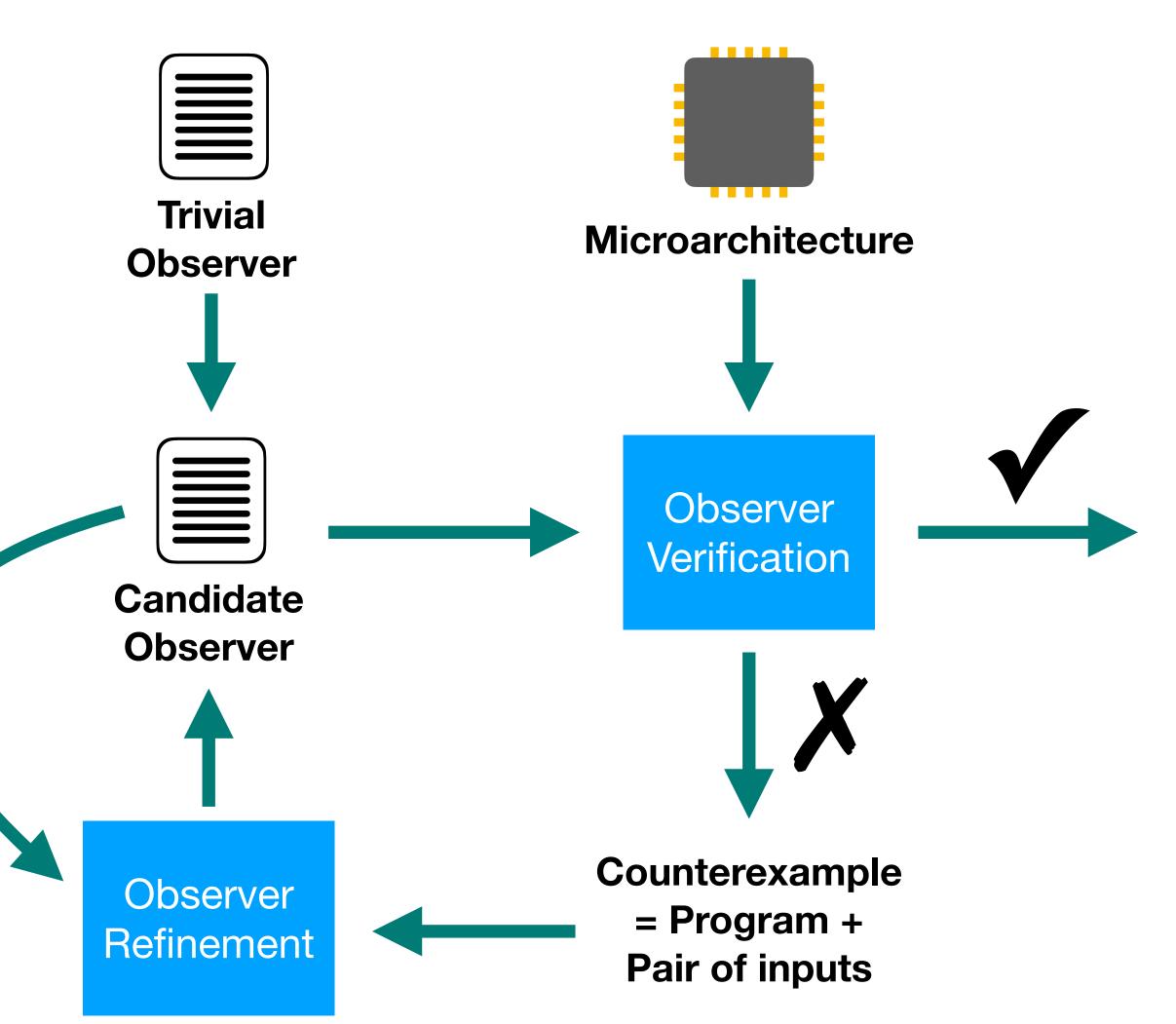

# **Observer Inference**

#### Microarchitecture

# Wanted:

Weakest Observer

# Conclusions

# Need to rethink hardware-software contracts with security in mind

### Find out more in our paper: M. Guarnieri, B. Köpf, J. Reineke, and P. Vila Hardware-Software Contracts for Secure Speculation S&P (Oakland) 2021